# PCIE 的一种测试方法研究

费晓华<sup>1</sup> 武新郑<sup>1</sup>

FEI Xiaohua WU Xinzhen

## 摘要

集成电路具有体积小、重量轻、寿命长和可靠性高等优点，同时成本也相对低廉，便于大规模生产，在电性能方面远远优于晶体管元件组成的电路。从第一款集成电路被研发再应用到生活中开始，在短短几十年的发展过程中，被广泛应用于军事、工业、通信和遥控等多个领域，这也标志着世界进入集成电路时代。目前集成电路的规模越来越大，集成的功能也越来越多，速度也越来越快。针对 PCIE 类型电路，基于 ATE 和测试仪器，对电路内部的 DFT 可测性进行系统的硬件设计和方法研究。

## 关键词

集成电路；ATE；PCIE；测试方法；DFT

doi: 10.3969/j.issn.1672-9528.2024.08.030

## 0 引言

2001 年，非营利组织 PCI-SIG 召集了英特尔、AMD、博通、IBM、微软等厂商提出了 PCIe<sup>[1]</sup> (Peripheral Component Interconnect Express) 新总线标准，此举是为取代旧的 PCI、PCI-X 和 AGP 总线标准<sup>[2]</sup>。2003 年，PCIE 1.0 技术正式产生，实现 2.5 GT/s 的传输速率。2006 年，PCIE 2.0 达到了 5.0 GT/s 的速率。2010 年，PCIE 3.0 将速率达到 8.0 GT/s。一直到 2022 年，PCI-SIG 正式发布了 PCIe 6.0，将传输速率翻倍达到了 64 GT/s。

可以看到，PCIE 的总线标准正在呈现指数级的上升，高速数据传输的能力已经成为提升数据传输速率的关键性因素<sup>[3]</sup>。由此带来的问题是，器件上如何提高传输的能力，以确保数据传输的准确性。对此问题，从两个方面来解决：一是针对工艺方面进行提高和改良，为满足复杂电路体积小、引线多、重量轻等特点，封装结构的合理性和科学性将直接影响集成电路的质量<sup>[4]</sup>；二是使用高速端口，利用其特性进行数据传输交换，来满足电路高速要求。SerDes 属于高速的数模混合电路，常集成在 PCIE 和 SATA 等 IP 核中<sup>[5]</sup>，它将芯片多路并行信号转换成单路高速串行信号，经过传输介质，再将高速串行信号重新转换成低速并行信号，减少了传输的通道数，保障了信号质量完整性。

本文基于 ATE<sup>[6]</sup> 测试，针对带 SerDes 端口的 PCIE 电路，对 DUT 器件进行系统的 DFT 可测性测试研究。

## 1 CP 测试

CP (chip probing) 测试指的是晶圆测试。CP 测试在整

个芯片制作的流程中，处于晶圆制造后、芯片封装前，晶圆 (Wafer) 制作完成后，其表面规则地分布着大量的裸 DIE (未封装的芯片)。在电路未封装前进行的 ATE 测试称为 CP 测试。为保障测试顺利进行，需要准备测试机 (Tester)、用于联通圆片的测试探针卡 (Probe Card) 和对应测试软件，如图 1 所示。本款 PCIE 电路中测探针选用钨针，它具有硬度、抗疲劳性好、寿命长的特点。此外，对于电流比较大的管脚，采用双针结构，并在测试程序中进行 DPS 限流的设置，防止针提前变黑老化。

图 1 探针卡

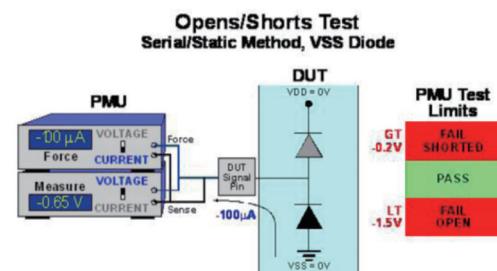

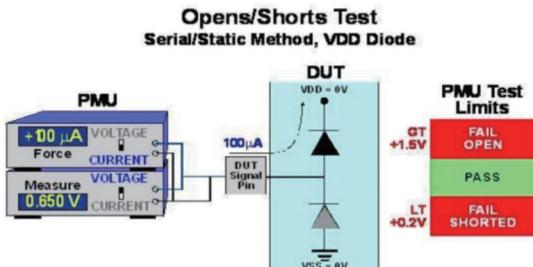

在 CP 测试中，主要进行 OS、扫描测试，对电路进行评估。OS 测试，选用 ADVANTEST 公司的测试机，检测下二极管是否导通，使用 PPMU 从 IO PIN 脚拉出一个 -100 μA 的小电流，检测二极管压降是否为 -0.7 V，检测上极管是否导通，如图 2 所示。使用 PPMU 从 IO PIN 脚灌入一个 100 μA 的小电流，检测二极管压降是否为 0.7 V，如图 3 所示。

图 2 -100 μA 电流

1. 中科芯集成电路有限公司 江苏无锡 214035

图 3 100  $\mu$ A 电流

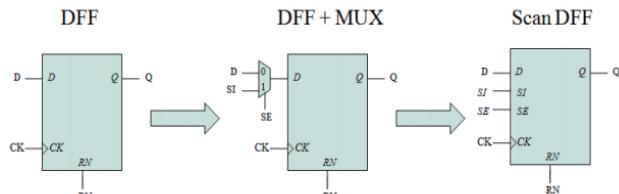

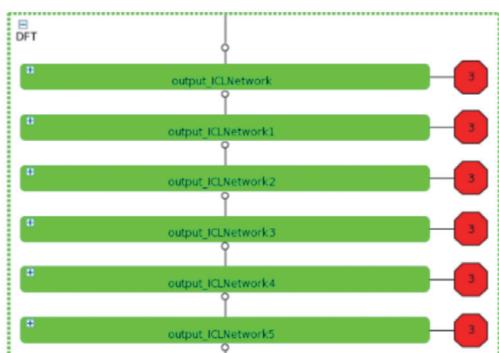

针对此款 PCIE 电路，为保障电路功能逻辑模块的准确性和 IO 脚与内部核心器件的正确性，需要进行扫描测试（scan chain）和边界扫描测试（B scan）。扫描测试是通过电路芯片内部的移位寄存器来判断其中电路是否正常，如图 4 所示。将多组移位寄存器的输入输出结果联系起来，就形成了扫描链测试，如图 5 所示。边界扫描同理也就是在电路的输入输出端口，增加一个寄存器，测试 IO 管脚的连接性是否正常。

图 4 寄存器

图 5 扫描链

## 2 FT 测试

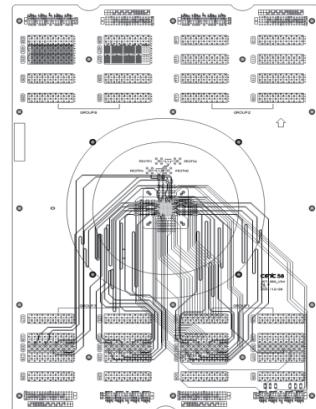

FT (Final Test) 测试是指芯片在封装完成以后进行的最终测试。PCIE 电路的主要功能和性能评估也主要在此阶段进行。首先需要保障的是硬件的设计和制作，主要体现在测试插座的选用和测试 Loadboard 的设计上。对于测试插座的选用，主要是接触管脚的针材质和形状，此款 PCIE 电路决定了针的材料必须满足高速 2.5 Gbit/s 以上，梅花型则保障了球形管脚的接触面足够大，保证了接触性良好。

在硬件（Loadboard）设计方面，采用罗杰斯高频板的材质，基板材料具有优秀的电性能、良好的化学稳定性。随着电源信号频率的增加，在基材上的损失要求非常小，保障了

良好的高频 2.5 Gbit/s 以上的信号完整性，如图 6 所示。

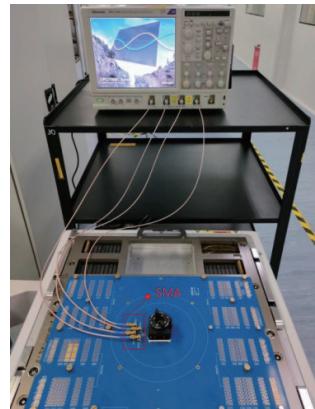

此外，在硬件设计过程中，高速信号和低速信号分开设计，最大限度保障互不影响。在 SerDes 传输信号过程中，将 4 链路信号设计成等长，在板上设计放在 SMA-KHD18G，便于高频线缆接到外部测试仪器，如图 7 所示。

图 6 测试板

图 7 SMA 设计

FT 测试是芯片出厂前的最后一道关，会对 PCIE 芯片做系统详细的检测，主要包括 BIST（内建自测试）、JTAG、loopback（内 / 外环路）测试、DC、AC、功能功耗测试。

## 3 BIST 测试

内建自测试根据测试对象的不同可以分为：存储器内建自测试（Memory BIST，MBIST）和逻辑内建自测试（Logic BIST，LBIST）<sup>[7]</sup>。MBIST 用于对存储器进行测试，判断内部存储器是否存在缺陷。LBIST 是针对数字逻辑部分的自测试方法，其同样将自测试电路集成到电路内部。根据此款 PCIE 电路的 BIST 真值表，如图 8，对应选取相应的测试模式。

| BIST_MODE[3:0] <sup>a</sup> | Mode Description                                        | Pass/Fail            |

|-----------------------------|---------------------------------------------------------|----------------------|

| 0000                        | PHY-Normal-operation, default value of BIST_MODE        | —                    |

| 1000                        | PHY-external-BIST from TXP/TXN to RXP/RXN               | BIST_OUT[1:0]=2'b11+ |

| 1001                        | PHY-internal-BIST                                       | BIST_OUT[1:0]=2'b11+ |

| 1010                        | PHY-send 1'b0-on-TXP-and-1'b1-on-TXN(only-for-VOL-test) | —                    |

| 1100                        | PHY-send 1'b1-on-TXP-and-1'b0-on-TXN(only-for-VOH-test) | —                    |

| Others                      | Reserved PHY-BIST-mode                                  | —                    |

图 8 真值表

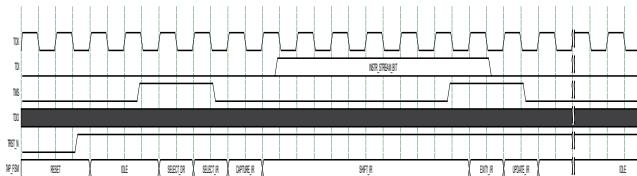

PCIE 电路的测试模式，信号激励是由 JTAG 端口打入，根据时序框图，如图 9 所示，开发出一套测试向量的测试软件，如图 10。将时序模板都固定下来，只需要测试人员填入所需的测试类型，即可快速得到 BIST 测试码进行测试。

图 9 时序图

图 10 测试码软件

#### 4 Loopback 测试

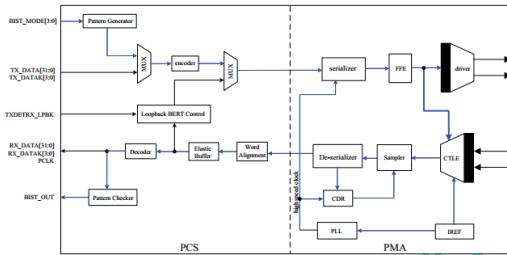

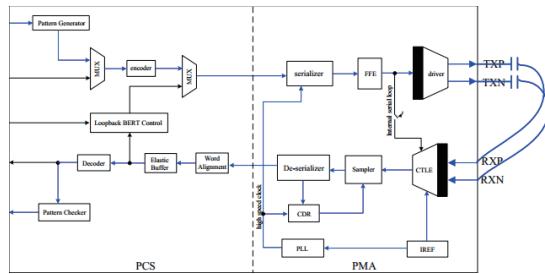

Loopback (环路) 测试是 PCIE 最重要的功能之一，环路成功表示 PCIE 的握手成功，以及之后数据交互正常运行，如图 11 所示。在 BIST 模式下选取对应 MODE 表生成向量。内环测试是将生成的测试码进行编码，并在 Loopback BERT 控制器作用下，经多路复用进行并转串行数据处理，从内部发送到采样器进行采样，然后经过串转并进行数据处理，最后经缓冲字节对齐后解码，做向量校对验收工作，以此实现内部环路结构进行自发自收。

图 11 电路结构图

外部环路功能，按照图 12 所示，数据经过 TX 发送到外部，PCB 测试板传输，RX 端口接收。

图 12 外环结构图

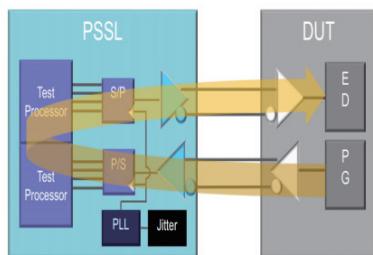

为了排除掉电路内部自运行的可能，确保走外部通路，本次特意设计了使用高速板卡 (PSSL) 进行数据中转，如图 13 和图 14 所示。

图 13 PSSL 环路

```

LOOPBACK_OPERATION_TASK lpb;

lpb.pin("OUT+").setOperationMode(LOOPBACK_OPERATION::PARAMETRIC_LOOP);

lpb.execute();

return;

```

图 14 loopback 打开

打开外部环路功能，机台接收 PRBS 伪随机测试码，经过 PSSL 板卡处理，如图 13 和 15 所示，再发送返回给 RX 端接收，DUT 校对测试接收的测试码。伪随机测试码的收发成功，体现在电路内部寄存器结果值从低变高，验证了环路测试的功能。

图 15 PSSL 工作原理

#### 5 参数测试

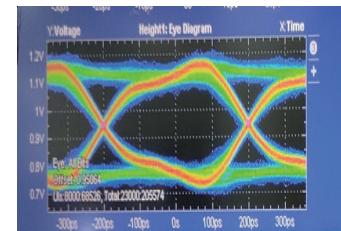

对于一款电路而言，参数测试能直观体现出 PCIE 电路的测试指标情况，DC 参数主要还是根据欧姆定律，使用测试机的 ppmu 测量单元，利用加压测流或者加流测压，能很快得出对应的测试结果。而 AC 参数主要针对的是时序类别的参数，对于低速部分本篇不多做讨论。针对高速参数，主要是高速 SerDes 脚，传输 PCIE 数据后，需要对其传输的速率、眼图、抖动、误码率等做出详细判断。

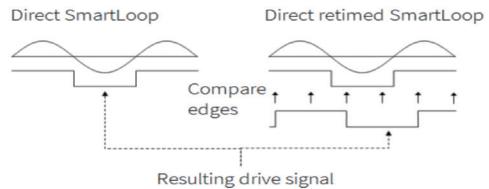

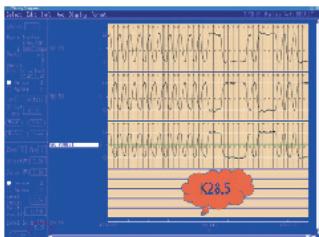

如图 7 所示，在 PCB 测试板上通过外挂 SMA 头，经过高频线缆的传输和转接头，连接外部仪器仪表。仪器选取泰克示波器的 7254C 系列，自带眼图和抖动功能，如图 16 和图 17 所示。在电路正常工作前，SerDes 脚发送 K28.5 码型，如图 18 所示，验证协议握手有效，电路正常工作，即可通过仪器读出参数指标。

图 16 泰克 7254C

图 17 眼图

图 18 K28.5 码型

此外,还可以通过新型测试方法,利用机台的特性,编写语句 JITTER\_INJECTION\_SET,选择对应待测 PIN 脚,主动给PCIE 电路注入抖动测试,测量其注入抖动后的承载能力。

## 6 误码率测试

误码率(SER)是衡量数据在规定时间内数据传输精确性的指标。在PCIE 电路测试中,要用误码率来判断电路的参数指标是否正常,误码率=传输中的误码/传输的总码数×100%。本文选用误码测试仪来进行测试,通过高频线缆接入误码仪,控制收发的PRBS伪随机测试码,如图19所示。此外,还可选取PRBS7、PRBS9、PRBS13、PRBS15、PRBS21等多种类型。

图 19 误码仪

## 7 电流测试

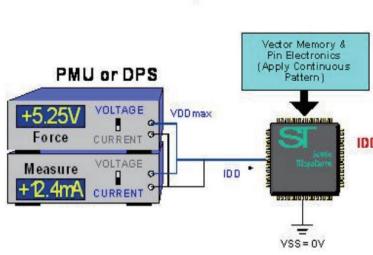

在PCIE 电路中,由于芯片规模集成大,大电流电路已经非常普遍。实现对大电流电路的测试是集成电路测试中一个十分重要的内容<sup>[8]</sup>。ATE 机台可选取多种电源,如MSDPS、DC SCALE、DPS32、DPS64 等。为了适应大电流特性,特意选取 DPS64 的电源板卡做测试,如图20 所示。

图 20 电源 DPS64

图 21 IDD 电流测试

动态是指器件处于活跃状态,如图21所示。动态电流测试就是指DUT在工作状态下流入VDD脚的总电流,通常会让器件活动在最高工作频率下,此时监测的电流就是DUT的最大工作电流,工作电流偏小的很大原因就是DUT未工作。由此,通过电流测试,可以清晰地确认电路工作是否处于正常状态,PCIE内部PHY的工作是否正常运行。

对于其余DC/AC参数测试,可以按照欧姆定律,通过加电压测电流、加电流测电压的方式得到,本文不做详细论述。

## 8 结论

目前PCIE电路多种多样,可测性方面也各有不同,如何根据自身特性进行相关的测试方案设计显得尤为重要。此外,随着大规模SoC<sup>[9]</sup>复杂类电路的兴起,传输速率越来越高,IP核的应用也越来越多,给DFT的设计和验证带来了巨大的挑战。DFT测试面较少,带来的后果就是测试覆盖率的降低,性能评估不全。

根据此款PCIE电路的测试方法介绍,本文提供了一套可测性的方法,可作为电路评估的模板。在今后的测试过程中,能全面保障电路的安全质量,做到有问题早发现。

## 参考文献:

- [1] 安立通讯科技(上海)有限公司. PCIe 5.0 SerDes 测试和分析 [J]. 中国集成电路, 2022(278):75-79.

- [2] PCIE 发展史科普篇 .(2023-01-01)[2024-02-03].<https://m.163.com/dy/article/HQ17078V0532B75P.html>.

- [3] 孙欣欣. 基于PCI Express的高速数据传输通道的设计与实现 [D]. 昆明: 云南大学, 2021.

- [4] 何磊, 冯佳, 李亚军, 等. 宇航级集成电路筛选过程质量管控措施 [J]. 电子质量, 2023(9):1-6.

- [5] 刘潇骁. SerDes 电路的可测性集成设计与机台测试 [D]. 长沙: 国防科学技术大学, 2013.

- [6] 上官星宸. 基于ATE的电源管理芯片的测试方法设计与实现 [D]. 成都: 成都理工大学, 2021.

- [7] 张俊腾. 基于PCIE IP核的可测试性设计与研究 [D]. 北京: 北京工业大学, 2015.

- [8] 赵桦, 王建超. 基于V93000 ATE的大电流测试方法研究 [J]. 电子与封装, 2017, 17(12):14-17.

- [9] 王大伟, 孙全, 杜春瑶, 等. SoC 芯片可测试性设计策略分析 [J]. 中国高新科技, 2023(15):18-19.

## 【作者简介】

费晓华(1994—),男,江苏江阴人,本科,工程师,研究方向:集成电路。

(收稿日期: 2024-05-17)