# 基于 3U/VPX 的高集成波形采集板设计与实现

杜晓敏<sup>1</sup>

DU Xiaomin

## 摘要

介绍了一种 3UVPX 标准波形采集板卡的设计，针对统型统标、不同应用场景、结构包络以及国产化需求，设计一种全国产化高集成波形多通道采集板卡。采用 3UVPX 标准架构实现通用化标准化，利用国产化芯片实现波形产生、数据采集以及信号预处理，最终实现单通道波形产生和 12 通道中频采集。硬件设计时钟可配置，从而实现 AD/DA 不同模式工作，简化了外部时钟的复杂度，使系统规范化、通用化、易于扩展使用，并缩短研发周期。通过关键指标的测试，验证了硬件平台的可行性与可靠性。

## 关键词

3UVPX；波形产生；采集；高集成；国产化

doi: 10.3969/j.issn.1672-9528.2024.08.029

## 0 引言

随着现代雷达向数字化、软件化、集成化方向发展<sup>[1]</sup>，以 VPX<sup>[2]</sup> 为代表的高速串行总线标准正逐步应用在现代雷达当中<sup>[3]</sup>，尤其在星载弹载产品中 3UVPX 标准板卡具有优良的导冷抗震性能和显著的重量体积优势<sup>[4-5]</sup>。同时，由于国际形势的日益紧张以及高端芯片对我国的禁售，研制基于 3UVPX 标准的国产波形多通道采集板十分必要。

## 1 系统设计组成

3UVPX 标准的国产波形多通道采集板基于标准化/通用化、全国产化、高性能、多通道高集成思路进行设计。

(1) 标准化/通用化：基于标准 3U/VPX 结构设计，采用 1 发 12 收多通道收发集成设计，可用于信号预处理相关模块，具有一定的通用性。

(2) 高性能：波形产生基于  $5 \text{ Gs}\cdot\text{s}^{-1}$  /14 位高性能 DAC 设计，可直接产生 1 GHz 瞬时带宽任意信号；数字接收基于 600 MHz/14 位四通道 ADC 设计，基于中频数字化数字解调输出高速率基带 I/Q 信号。

(3) 多通道高集成：宽带波形采集采用 1 发 12 收单个 3U/VPX 标准板卡集成设计，实现大于 1 GHz 波形产生和大于 200 MHz 带宽宽带接收；多通道波形采集采用 1 发 12 收单个 3U/VPX 标准板卡集成设计，实现大于 1 GHz 波形产生和大于 200 MHz 带宽接收；ADC/DAC 时钟产生板级集成设计。

(4) 全国产化：板卡设计均采用国产元器件，实现 100% 国产化设计。

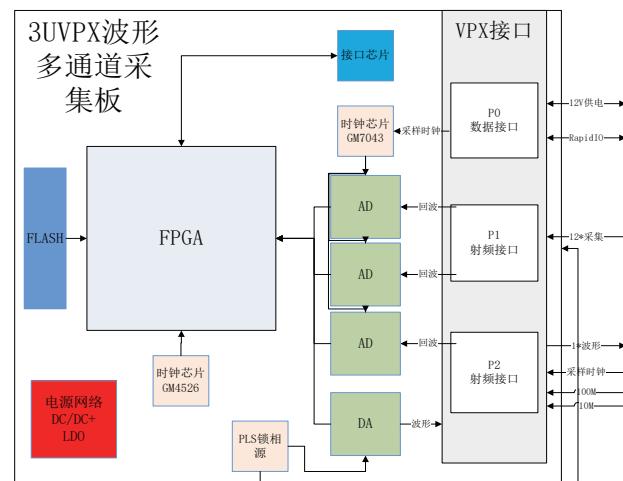

波形多通道采集板采用标准 3U/VPX 结构形式，基于中频数字化收发体制设计<sup>[6]</sup>，板上集成 12 通道宽带采集和单通道宽带波形产生，并通过背板上的混装连接器与机箱内/外其他设备进行互连。波形多通道采集板原理框图如图 1 所示。

图 1 波形多通道采集板组成框图

## 2 硬件电路设计

### 2.1 AD 电路设计

AD 电路是多通道波形采集板的核心电路，多通道波形采集板需要集成 12 路采集通道，考虑到指标和 12 路集成设计，ADC 选择杭州城芯公司 14 位 750 Ms/s 四通道芯片 CX7442 进行设计<sup>[7]</sup>。CX7442 是一款集成高速高精度 4 通道 ADC 以及基于 JESD204B 子类 1 标准 SerDes 接口，集成中、射频信号处理系统芯片。最高采样率为 750 Ms/s，数据位宽 14 bit。

1. 中国电子科技集团公司第三十八研究所 安徽合肥 230088

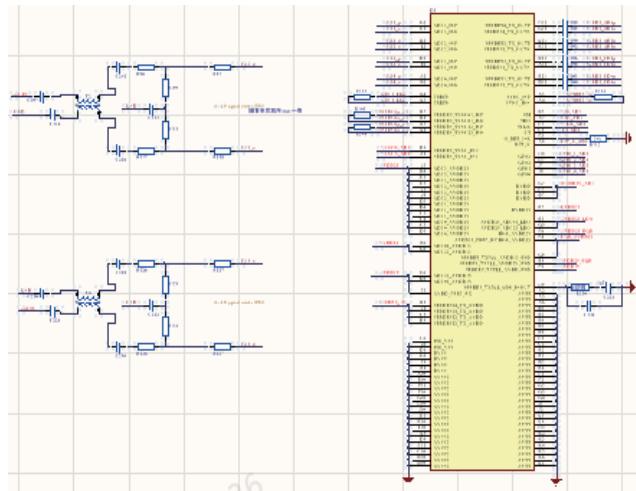

波形多通道采集板集成 3 片 CX7442。单片 CX7442 芯片电路设计如图 2 所示。电源端口 DVDD25 选择供 1.8 V 电平，SPI 配置端口输出 COMS1.8 V 电平标准可以和 FPGA 直接通信。为达到 AD 采集的最佳性能 (SNR 和 SFDR 指标)，射频前端部分采用差分耦合以抑制大多数放大器的噪声影响。FREFP/FREFN 为采样时钟输入端口，采用 AC 耦合。SYNC\_INP/SYNC\_INN 为 sysref 输入信号端口，中间短接 100  $\Omega$  电阻，采用 DC 耦合。该芯片 SYNC 信号发送有两种模式，既可以采用差分信号 SERDES\_SYNC\_INP/SERDES\_SYNC\_INN，也可以采用单端信号 SERDES\_SYNC\_IN，可以都接进 FPGA。CX7442 电源品种有近 20 种。为简化电源供电网络、降低成本，将电源品种划分为 4 大类模拟电：AVDD (1.0 V、1.3 V、2.5 V) 和数字电 (1.0 V)，每一类分别有一个 LDO 供电，这样设计可以在不影响 AD 性能的情况下显著简化供电网络，降低设计难度。

图 2 AD 电路设计

## 2.2 DA 电路设计

波形多通道采集板具备产生 1 GHz 带宽信号的直接产生能力，同时具备生成 LFM 信号、PSK 信号等调制信号的产生能力。根据现有国产化器件水平，选择振芯科技的 14 位 5 Gs/s 转换速率单通道 DAC 芯片 GM4817<sup>[8]</sup>，芯片集成 12 路最高速率为 6.25 Gbit/s 的高速 Serdes 接口进行数据接收，接口支持 JESD204B 标准中的 8B/10B 解码及多 lane 同步。另外，该芯片集成 RF-DAC 直接射频混频功能。指标如下。

- (1) DAC 最高采样率：5 Gs/s

- (2) DAC 数据位宽：14 位

- (3) 宽带杂散： $\geq 50$  dB

- (4) 窄带杂散： $\geq 85$  dB

- (5) 微分非线性误差： $\leq \pm 4$  LSB

- (6) 积分非线性误差： $\leq \pm 6$  LSB

## (7) 功耗： $\leq 2$ W

GM4817 内部集成带自偏置的差分输入放大器，最高支持 5 GHz 时钟输入，为减少时钟品种，采用 13 所 PLS 系列锁相源产生高性能使时钟作为 DA 芯片的转换时钟。使用 1:1 balun 提供差分时钟输入，AC 耦合方式，同时在 PCB 布板时，balun 尽量靠近 PIN 脚连接，以减少 PCB 板级寄生电感、电阻、电容对输出性能的影响。

GM4817 芯片有四组电源，分别为 DVDD12、AVDD12、DVDDIO、AVDD33，采用独立的稳压芯片供电，以获得高的杂散性能指标。

DAC 输出模式包括常规模式 / 非归零模式、归零模式、混频模式和内插模式等，通过不同输出模式，选择可以实现 3 ~ 4 个 Nyquist 带的信号输出。本设计采用内插混频模式，以实现较高的中频产生。

## 2.3 时钟电路拓扑

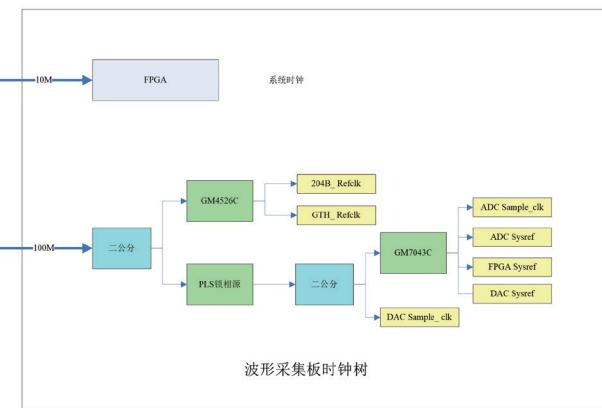

波形多通道采集板设计 ADC/DAC 时钟、内部高速口参考时钟以及 JESD204B 接口确定性时延同步时钟等都是基于板级一体化集成设计实现，外部只需提供参考时钟即可。基于 PLS 锁相源，GM7043C 和 GM4526C 产生采样时钟、低抖动高速口参考时钟、时延稳定和精确可调确定性时延同步时钟。PLS 锁相源基于可以实现表贴小体积高性能固定点频源。GM7043C 为成都振芯研制对标 ADI 公司的 HMC7043 时钟扇出芯片。

波形多通道采集板时钟设计基于板内一体化设计，外部只需要 10 M/100 M 时钟。10 M 时钟作为系统时钟输入 FPGA 作为本地全局时钟；100 M 时钟共分两路，一路作为 PLS 锁相源输入产生高频信号，一路作为 GM4526C 的参考输入产生多路 GTX/GTH/204B 所需要的参考时钟。PLS 输出时钟，一路作为 DA 的转换时钟，一路作为 GM7043C 的输入时钟，由 GM7043C 产生 3 片 AD 芯片的采样时钟和 sysref 信号，以及 DA 的 sysref 信号，如图 3 所示。

图 3 时钟拓扑

### 3 软件设计

#### 3.1 基于 ADC+FPGA 的 DDC 设计

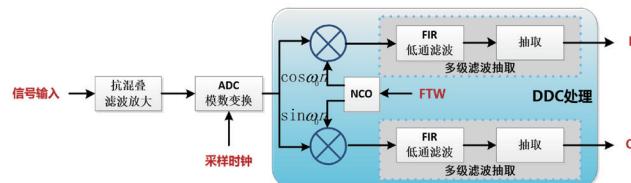

数字化接收处理基于软件无线电思想, 实现数字下变频 DDC 处理(包括数字解调、数控振荡器 NCO 和多级可编程高效滤波抽取等多速率信号处理)的数字中频/射频多速率信号处理。与高速高性能 ADC 相结合, 可以实现工作频带内任意频点、多种带宽信号的数字解调和滤波处理。基本实现原理框图如图 4 所示。

图 4 基于 ADC+FPGA 的 DDC 处理原理框图

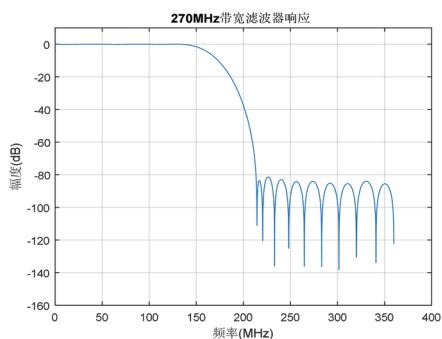

图 5 给出了 270 MHz 和 20 MHz 两种典型带宽 DDC 滤波器设计频率响应仿真结果。

(a) 270 MHz 带宽 DDC 处理滤波器响应

(b) 20 MHz 带宽 DDC 处理滤波器两级级联响应

图 5 典型 DDC 处理滤波器设计频率响应仿真结果

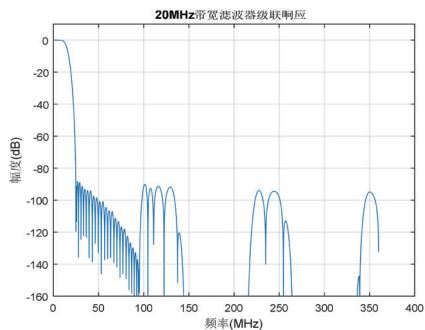

#### 3.2 基于 FPGA+DAC 的 DDS/DUC 设计

数字化信号任意产生可以基于 DDS 技术和 DUC 技术来产生。DDS 以其接口简单、控制灵活、低功耗、高集成度等特点, 已经广泛应用于雷达、通信等系统中。目前雷达工作方式要求信号具有多种波形形式, 要想改变信号的频率、脉宽、带宽等参数, 就要求雷达的波形形成非常灵活, 而 DDS 恰能满足这一要求。

DDS 可以对输出波形信号的频率调节字 FTW、调谐率 DTW、相位调节字 PTW 和幅度调节字 ATW、信号脉宽 PW 等一个或多个参数同时进行直接调制, 能够实现目前雷达的各种调制方式信号产生, 如点频、LFM、NLFM、xPSK、双斜率 LFM、捷变频信号、步进频信号等。因此, 基于 DDS 技术方式可以满足本雷达需要的各种发射信号和掩护脉冲信号产生的需要。图 6 给出了 DDS 的基本原理框图。

图 6 DDS 基本原理框图

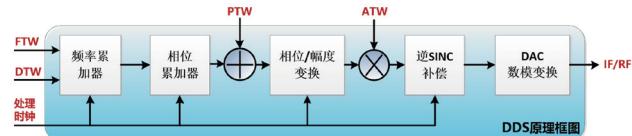

DUC 技术是通过对基带数据进行插值、滤波和数字混频的方式产生波形信号, 理论上可以产生任意波形信号。其结构灵活、波形可任意配置、具备预失真补偿能力, 因此该技术已大量应用于雷达、通信、电子战等宽带多功能一体化系统设计中, 实现软件定义的任意信号产生。基于 DUC 技术的任意信号产生是基于 DDC 处理技术的数字接收的逆过程, 其基本原理框图如图 7 所示。

图 7 任意信号产生 DUC 处理基本原理框图

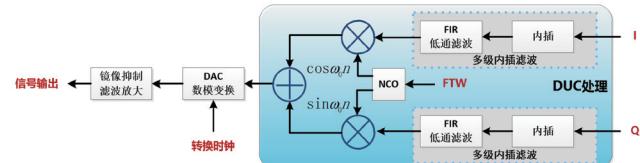

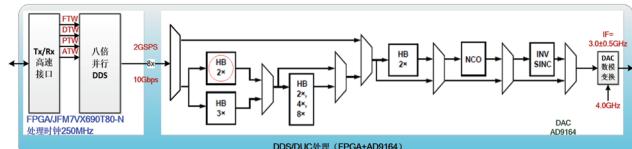

信号产生基于 FPGA+DAC 的 DDS/DUC 方式产生雷达需要的各种信号, 基于 FPGA 的并行 DDS 可以产生正/负调频 LFM、PSK 等各种调制基带 I/Q 信号, 该基带 I/Q 信号送入 GM4817 芯片, 在 GM4817 芯片内再进行数字上变频 DUC 处理和数模转换 DAC 处理, 最终输出需要的雷达中频波形信号。整个信号产生流程原理如图 8 所示。

图 8 基于 FPGA+DAC 的 DDS/DUC 信号产生流程框图

信号产生时 FPGA 内部通过 8 倍并行 DDS 产生 2 Gs/s 速率基带 I/Q 信号, 通过 FTW/DTW/PTW 等设置产生宽带正/负调频 LFM 信号、宽带掩护脉冲信号、宽带相位编码信号, 该基带信号通过 JESD204B 接口传输给 GM4817, 片内二倍内插滤波到 4 Gs/s 速率基带信号、再通过 DUC 输出中频数字信号。基于 GTH 高速串行接口传输速率 5 Gbit/s, 参数传输到信号产生输出时间远小于高重复频率工作的重复周期(25 μs/40 kHz),

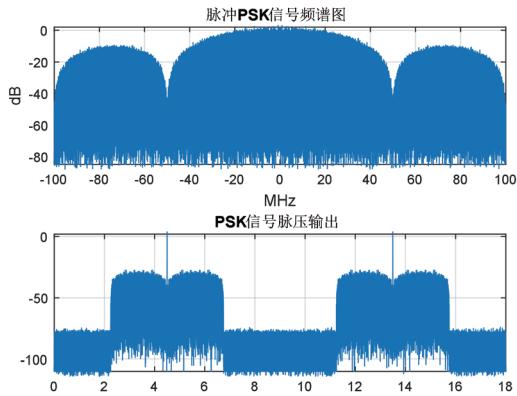

因此本方案也可以实现高重频信号产生。图 9 给出了相位编码信号仿真结果（基于平方余数序列二相码）。

图 9 相位编码信号产生仿真

(BW=50 MHz / PW=28  $\mu$ s / PRF=5 kHz)

### 3 关键指标测试

本章节主要对波形多通道采集板进行 AD/DA 性能的测试，根据文献 [9-10] 介绍的高速 ADC 性能参数的测试相关方法，进行 ADC 和 DAC 性能测试：无杂散动态范围（spurious free dynamic range, SFDR）、信噪比（signal to noise ratio, SNR）。将信号源分别设置 650 MHz、750 MHz、850 MHz、950 MHz 单音信号进行测试，见表 1。为了取得较好的测试结果，需要抑制信号源的谐波，可以将信号源接入一个截止频率为 1000 MHz 的低通滤波器，再接入采集通道。

表 1 ADC 性能测试

| 测试频点 /MHz | SNR/dB | SFDR/dB |

|-----------|--------|---------|

| 650       | 55.28  | 72.66   |

| 750       | 54.66  | 70.52   |

| 850       | 53.21  | 69.58   |

| 950       | 51.86  | 68.32   |

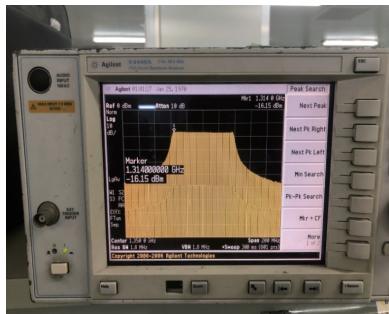

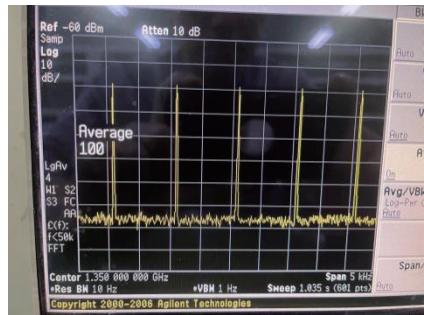

对 DAC 的各个通道进行性能测试，主要测试 DAC 的脉内信噪比和线性调频信号的带内平坦度。设置 DAC 转换速率为 4 Gs/s，混频模式，DDS 设置 1 GHz 带宽 50  $\mu$ s 脉宽的脉冲线性调频信号，重频 5 kHz。将信号接入频谱仪中，可以观测到该线性调频信号平坦度小于  $\pm 1.5$  dB，脉内信噪比大于 50 dB，如图 10 所示。

(a) 1 GHz 带宽带内起伏

(b) 脉内信噪比

图 10 波形测试结果

### 4 结论

本文提出了一种高集成全国产化的波形多通道采集设计方案，基于标准 3UVPX 架构实现高性能高集成满足多种应用场合。文章介绍了硬件电路设计和软件关键架构，并通过关键指标的测试验证了方案的正确性。

本硬件方案通过对时钟的不同配置和不同频点锁相源的原位替代，满足对数字收发的多种需求，从而实现信号处理系统的快速迭代，缩短研发周期，这体现了方案的优越性。

### 参考文献：

- [1] 高环. 现代相控阵雷达技术发展 [J]. 现代导航, 2023(5):368-375.

- [2] RODRIGUES A P, PEREIRA L, MADEIRA T I, et al. Real-time multi-DSP based VME system for feedback control on the TCV Tokamak [J]. IEEE transactions on nuclear science, 2006, 53(3): 845-848.

- [3] 陈昌明. 基于 VPX 的高速信号采集处理卡的设计与应用研究 [D]. 郑州：解放军信息工程大学, 2016.

- [4] VPX 高可靠性军用加固通讯计算平台 [J]. 国防制造技术, 2011(3):11.

- [5] 蒙俊. VPX 抗恶劣环境通信计算平台关键技术研究 [J]. 测控技术, 2012, 31(10):88-91+97.

- [6] 熊淳, 张荣福. 基于 FPGA 的雷达信号采集系统设计 [J]. 光学仪器, 2021, 43(4):78-85.

- [7] CX7442 数据手册 v2.1[Z]. 城芯科技, 2023.

- [8] GM4817 数据手册 [Z]. 振芯科技, 2019.

- [9] 林源泉. 高精度高速 ADC 测试方案设计与实现 [D]. 成都：电子科技大学, 2020.

- [10] 何江涛. 基于数字信号处理的高精度 ADC 测试方法研究 [D]. 成都：电子科技大学, 2019.

### 【作者简介】

杜晓敏 (1989—)，男，山西大同人，硕士，工程师，研究方向：数字收发。

(收稿日期: 2024-06-10)