# 基于 FPGA 的自制测试系统

朱清<sup>1</sup> 张尧<sup>1</sup> 张卯<sup>1</sup>

ZHU Qing ZHANG Yao ZHANG Mao

## 摘要

针对芯片测试整个流程消耗 ATE 设备机时较多的问题, 提出一种自制自动测试架构系统, 基于主控系统、FPGA 互连系统和上位机监控系统, 利用 FPGA 内部逻辑电路可配置特点实现了测试流程的自动化。在实际应用中, 显示测试流程简单, 监控上位机界面友好, 证明了所设计的系统的可行性。监控系统实现了芯片整个测试流程的透明化及全流程可追溯, 保证了测试的可靠性, 极大释放了 ATE 的占用时间, 提高了整体的测试效率, 降低了测试成本。

## 关键词

芯片; 自动化测试; 实装板; FPGA; 测试系统

doi: 10.3969/j.issn.1672-9528.2024.08.022

## 0 引言

随着国产化 MCU 芯片的崛起, MCU 芯片种类日益繁多, 从新封、筛选、考核到入库, 芯片测试<sup>[1]</sup>一直存在于芯片的整个生产过程中。ATE 机器<sup>[2]</sup>的测试时间非常宝贵, 测试人员的开发时间和测试时间也很有限, 由于成本原因, 整个测试流程仅仅靠 ATE 完成显得非常紧张, 导致很多芯片的量产成为棘手的问题。释放部分 ATE 测试机器的测力成了芯片公司关注的一个问题。

常用的 ATE 测试设备有 Teradyne 的 FLEX 系列和 Advantest 的 T6682、V9300 等, 尽管目前 ATE 设备的通道数量有了可观的增加, 也具备了 ATE 设备可以同时进行多芯片测试的特点, 但是数量还是很难满足需求。另外, ATE 的开发环境较为独立, 相应的技术人才储备速度较慢, 开发流程较为繁琐。传统的板卡级测试方案<sup>[3-5]</sup>布局复杂, 外接接口较多, 另外有时还需要外挂仿真器串口等设备, 导致测试稳定性较差, 并且传统板卡级测试方法可复制性较差, 导致测试

开发成本很高。

基于以上原因, 本文提出了自制实装板一键测试系统方案, 将芯片功能测试和部分性能参数测试从传统的 ATE 转移到实装板上进行系统性测试。该方案通过设计通用测试架构, 构建一个符合 MCU 的测试系统, 专注于方案的可复制性, 且开发成本小。并且对芯片 MSP430F169 进行了方案的验证。

## 1 系统架构设计

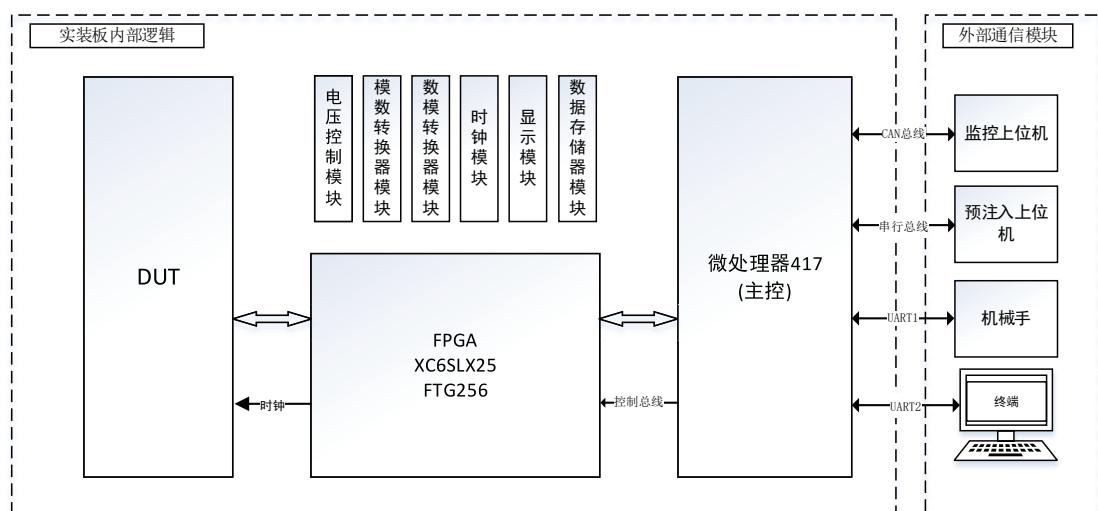

本文提出的实装板测试系统架构基于 FPGA+ARM, 主要有主控系统、待测端 (DUT) 软件集、互连子系统、监控记录系统、文件注入系统五个主要组成部分。方案架构如图 1 所示。

图 1 主控系统框图

### 1.1 主控系统

主控系统的功能主要有电源模块的控制、DUT 的程序下发、FGPA 网表的注入、DUT 的测试、DUT 的 ID 读写以及测试结果的上传等功能。

电源模块的控制部分主要是 DUT 的电源电压、模拟芯片的电压以及外围芯片的电压控制。DUT 的测试往往需要多电压可调节测试，实现程序化控制电压的方案，增强了测试的电压可调节范围和自动化程度。

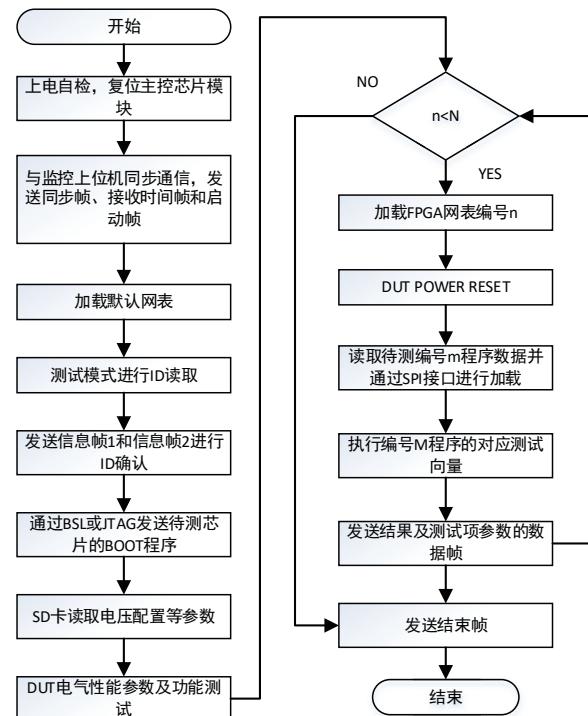

DUT 的程序和 FPGA 网表的程序由文件注入系统通过上位机下发至 SD 存储卡的指定扇区中，并且往 SD 卡中注入程序的信息预载。本方案使用多待测程序对应单 FPGA 网表，将复用不冲突的管脚功能放在一个 FPGA 网表中实现。由于互连测试管脚切换组合较多，一个单独的 FPGA 网表不能包含所有组合，而且为了降低测试程序间的耦合，采用多个网表进行动态切换的方案。

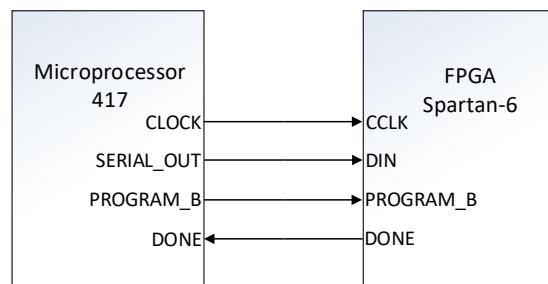

DUT 与主控系统间的通信总线为 SPI 总线<sup>[6]</sup>。SPI 总线是一种高速的全双工同步的通信总线，并且在芯片的管脚上只有四根线，节约了芯片的管脚，同时为 PCB 的布局提供了方便。主控系统通过 SD 卡读取预载信息进行测试程序读取并通过总线进行程序的下发。FPGA 网表的下发通过控制 FPGA 的模式引脚来使其作为 SPI 从机与主控系统进行数据交互，实现网表的自动化下载。

主控系统另外一个重要的功能是测试结果和测试数据的上传，与监控上位机软件交互的接口为 CAN 总线接口<sup>[7]</sup>。由于实装板与外部设备需要进行数据结果的交互，且处于工业生产环境，需要总线具有传输距离远、抗电磁干扰能力强的特点，而这些特点 CAN 总线都具有，并且 CAN 总线还有可靠的错误处理和检错机制，非常适合用于工业生产中的即时通信。本方案中使用的 CAN 传输帧都为扩展帧，原型帧 ID 为 29 bit，原型帧数据段为 64 bit，整个过程通信帧主要分为同步帧、时间帧、启动帧、信息帧、接口状态帧、功能状态帧、功能数据帧、结束帧。

### 1.2 监控系统

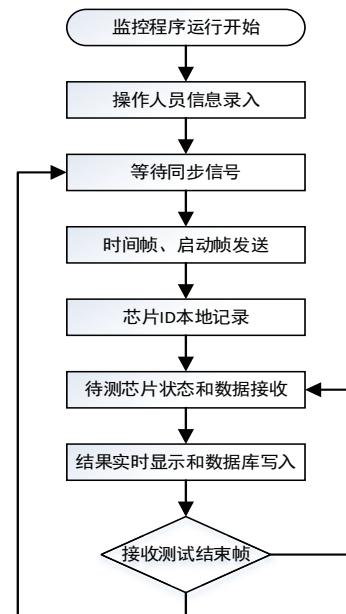

监控系统负责与下位机主控系统进行命令和数据交互，包括操作人员信息录入、同步、启动、ID 的写入、待测芯片的状态、待测芯片测试结果、功能项的数据记录、数据库的加密等功能。另外，监控系统也支持本地测试项结果的查询，根据指定条件进行数据项分析与显示。监控系统的流程如图 2 所示。

图 2 监控上位机流程图

### 1.3 待测端软件集

待测端软件集指 DUT 的 BootLoader 和测试用例。由于部分 MCU 芯片的 BOOT 接口只支持 UART 接口，传输数据的速率较慢，严重影响测试的时间和效率。本方案提出 MCU 与主控系统之间的通信宿主为 MCU 的二次 BOOT，通信接口可以根据具体的 DUT 和主控系统做调整，本方案使用 SPI 接口进行传输，通信速率最高可达 4 MHz。BootLoader 的主要作用是将通信接口接收到的测试用例二进制数据写入程序对应的物理地址，包括写入中断向量的重定向数据。

### 1.4 文件注入系统

由于主控芯片的 FLASH 空间大小有限，一般为 10 M 以内，而 FLASH 网表的 BIN 文件较大且有多套网表二进制文件，主控芯片自带 FLASH 不能满足数据的存放，而 SD 卡具有高记忆容量、数据传输速度块快、体积小等优点，可用于存储测试程序和网表 BIN 文件。文件注入系统通过上位机进行待测程序和网表程序的文件整合并预加载至 SD 卡的指定扇区，主控系统根据预载信息进行程序读取并下发。

### 1.5 互连子系统

本文采用 FPGA 作为互连子系统的控制器件，其主要作用是产生 DUT 的时钟输入、管脚的重映射等功能。FPGA 器件的时钟管理模块具有低噪声高灵活度的时钟控制，数字时钟管理器（DCM）可以消除时钟歪斜和占空比失真，锁相环（PLL）可以实现低抖动时钟控制，频率综合实现倍频分频和调相。通过 FPGA 器件的时钟输出管脚，可以为 DUT 提供稳定的可变时钟。

## 2 系统硬件设计

本文基于待测 32 位微处理器芯片 MSP430F169 进行硬件方案设计。

主控系统芯片选用 STM32F417, STM32F4xx 系列基于高性能 ARM Cortex-M4 32 位 RISC 核架构, 最高主频可以达到 168 MHz, 具有一个浮点运算单元 (FPU), 支持所有 ARM 单精度数据处理指令和数据类型, 并且实现了较全的 DSP 指令集和内存保护单元 (MPU), 增强了应用的安全性。该处理器支持最多 3 路 I2C, 3 路 SPI, 4 路 USART 加两路 UART, 两路 CAN, 一个 SDIO 标准接口, EMAC 等外设资源, 支持 FSMC 扩展接口。另外, FLASH 容量可达 1 MB, SRAM 容量可达 192 kB。该芯片的片上资源为测试系统的实现提供了较为灵活的方案选择。

互连子系统的 FPGA 芯片选用 XILINX 公司的 Spartan6 系列芯片。由于待测 32 位微处理器的管脚为 64, 所以本实验方案按照成本最小化和性能综合评估后选择 XC6SLX25T 器件。该器件具有 24 051 个逻辑单元、229 kB 的分布式 RAM、190 个 I/O 等资源, 对于 64 管脚 MCU 芯片测试资源能够满足。

电压控制模块的功能主要是通过电压控制芯片来控制 DUT 的上电电压, 控制 FPGA 的 IO 端口的 BANK 电压, 还具有控制 DUT 测试芯片的模拟参考电压的功能。数据存储器模块主要包含 FSMC 接口的 SRAM, SDIO 接口的 TF 卡等。模数转换模块测试<sup>[8]</sup> 使用 18 位精度的 MAX5318 作为 DUT 输入源, MAX5318 芯片控制接口为 SPI 接口, 输出电压最高 5.9 V 完全满足 MSP430F169 的 ADC 性能参数 INL 和 DNL 的测试条件。数模转换模块测试<sup>[9]</sup> 使用 16 位精度的 ADS8422 作为 DUT 的 DAC 输出的采样芯片, 该芯片是全差分输入, 最高输入频率为 4 MHz, 满足 DUT 的 DAC 性能参数的测试。

测试系统的具体硬件如图 3 所示, 1 代表主控芯片, 2 代表 FPGA 芯片, 3 代表 DUT, 4 代表电源模块, 5 代表模拟电路模块, 6 代表存储介质, 7 代表 CAN 接口, 8 代表串口接口。

图 3 实装板硬件系统

## 3 系统软件设计

软件设计主要包括主控软件、上位机监控软件、注入系统以及互连子系统的设计。整个软件系统设计遵循的原则为自动化与可靠性, 具有超时处理的特点, 可以实现尽量少的人工干预。

主控系统的程序设计具体流程如图 4 所示。

图 4 主控系统控制流程图

互连子系统的软件设计主要是 FPGA 内部互连逻辑、时钟产生模块的设计。互连逻辑的切换为 FPGA 输入信号即主控系统产生的组合信号控制。生成的网表个数由 DUT 的片上资源规模决定, 原则是尽可能将相同模块及不同功能管脚定义为一个网表。多个网表对于整个系统测试的复杂度和覆盖度有很大的提升。多网表可以将待测芯片的管脚复用测试更加全面, 验证程序可以更加多样化, 使软件编程难度降低。FPGA 网表下载模式如图 5 所示。

图 5 FPGA 网表下载模式

监控系统主要使用 Python3.7.0 语言开发, 使用多线程技术以及 SQLite3 轻量级数据库<sup>[10]</sup> 实现了测试状态的显示、测

试过程的记录以及测试结果的查询，并且使用数据库加密技术实现了数据记录的安全性。多线程保证了整个监控上位机能够实时接收主控系统上传的信息和数据，能够保证显示的实时性，同时也保证了系统的稳定性。

#### 4 实装板验证

在上位机运行状态下，对主控系统施加外部 6.5 V 电源电压供电，主控系统与其他子系统开始通信，实施整个测试流程。如图 6 所示，整个测试流程全部界面化与自动化。

图 6 上位机监控系统显示界面

关于监控状态的显示，测试人员主要关注测试开始时间、状态以及测试板卡号。当前方案中支持最多 32 块实装板并行测试。当界面中的状态显示超时或者失败时，说明当前板号所测试芯片有异常情况，需要进行异常分析。

整个测试过程监控系统不需要关闭，只需要通过测试人员或者外部机械臂进行实装板的供电和芯片更换即可。

表 1 为本实装测试系统方案与 ATE 测试机对同一待测芯片的主要测试参数对比，待测芯片型号为 MSP430F169 型 12 位微处理器。由表 1 中数据可以看到，本实装测试方案频率、占空比、建立时间、ADC 性能参数的测试精度可以替代 ATE 测试机进行 DUT 筛选测试。

表 1 测试参数和结果比较

| 参数                | ATE 测试机 | 实装板 DUT1 | 实装板 DUT2 | 实装板 DUT3 |

|-------------------|---------|----------|----------|----------|

| 频率 $f_{DCO}$ /MHz | 1.149   | 1.150    | 1.144    | 1.145    |

| 占空比 $D_{DCO}$ /%  | 49.586  | 49.878   | 49.760   | 49.763   |

| 建立时间 SR(μs)       | 27.1    | 39.28    | 36.92    | 35.61    |

| ADC INL(LSB)      | 5.86    | 1.95     | 2.00     | 2.63     |

| ADC DNL(LSB)      | 2.85    | 1.92     | 2.37     | 1.99     |

| 功能集测试             | 通过      | 通过       | 通过       | 通过       |

#### 5 结语

本文基于 FPGA 和 MCU 架构实现了实装板自动化测试架构的实现，并且加入监控系统实现了芯片整个测试流程的透明化，包括测试人员和测试环境的可追溯性。同时，实装板系统测试方案释放了测试机的大量机时、测试人员的测试时间，实现了降本增效。由于 DUT 芯片种类较为复杂，在选择主控芯片时，需要将变化的部分做独立分析，开发出合适的接口，必要时可以在主控系统与外部控制端之间加入转接系统，实现整个通信接口的兼容性和可复制性。

#### 参考文献：

- [1] 王俊, 方燕飞, 李岱峰, 等. 大规模芯片测试系统的研究与实现 [J]. 计算机工程, 2012, 38(16):233-236.

- [2] 康培培, 陈诚. 基于 ATE 的 CPLD 测试方法研究 [J]. 电子质量, 2021(10):31-35.

- [3] 袁江煜. 基于 LabVIEW\_FPGA 的板卡自动化测试系统设计与实现 [J]. 电子元器件与信息技术, 2020, 4(11):233-236.

- [4] 谢林峰, 何敏, 李文鑫. 面向 DSP+FPGA 通用处理架构检测的硬件系统设计 [J]. 电子制作, 2021(21):11-14.

- [5] 石英, 陈心浩, 何湘竹. 基于“单片机+FPGA”的数字芯片自动测试系统设计 [J]. 实验技术与管理, 2020, 37(12): 138-143.

- [6] 张凯虹, 武新郑, 武乾文. 内嵌于 DDS 的 DAC 线性参数测试 [J]. 电子与封装, 2012, 12(5):11-13.

- [7] 田智春, 负卫国. 基于嵌入式数据库 SQLite 3.0 的远程监控系统 [J]. 工业控制计算机, 2010, 23(3):36-37.

- [8] 田辉, 游有鹏. 基于 SPI 总线的 ARM 与 DSP 通信协议设计 [J]. 工业控制计算机, 2015, 28(1):62-66.

- [9] DOERNBERG J, LEE H S, HODGES D A. Full-speed testing of A/D converters [J]. IEEE journal of solid-state circuits, 1984, 19(6):820-827.

- [10] 张莉. 基于 CAN 总线的通信系统设计研究 [J]. 自动化与仪器仪表, 2018(4):91-94.

#### 【作者简介】

朱清 (1991—)，男，江苏扬州人，本科，工程师，研究方向：集成电路验证及板级数模混合电路测试。

(收稿日期：2024-07-02)