# 基于多核 DSP 的多路信号并行参数测量软件设计

苏 龙<sup>1</sup> 闫吉忠<sup>1</sup> SU Long YAN Jizhong

摘要

在通信电子战中,为满足大宽带、高实时性条件下信号参数测量的需求,设计了一种基于多核 DSP 的多路信号并行参数测量方法。首先对信号参数测量原理、核心算法和软件运行环境进行了介绍,其次详细描述了软件设计方案以及在多核 DSP 上内核控制模型、内核通信机制、存储分配和程序设计及优化四项关键技术上的实现方法,最后结合硬件平台对软件进行了测试,并对多核参与并行测量的加速比进行了对比分析。实验结果表明,所提出的软件设计可行、高效,为下一步宽带扩展及应用场景升级奠定了基础。

关键词

多核 DSP: 信号参数测量: 多路: 并行: 核间通信

doi: 10.3969/j.issn.1672-9528.2024.06.035

## 0 引言

在通信电子战中,信号参数测量作为信号处理的关键技术,是通信情报破译和电子进攻选择的依据。在宽带复杂电磁环境下,往往需要同时对多路信号进行处理,以传统单核 DSP 芯片为核心的实现方案处理速度已无法满足实时性的要求,且对处理信号的带宽、调制样式等有多种限制。随着 DSP 芯片的快速发展,芯片的处理能力有了很大的提升。TMS320C6678 DSP 芯片集成了 8 个内核,相当于同时使用8 片芯片,每个内核都拥有 32 kB 的 L1 程序缓存、32 kB 的 L1 数据缓存和 512 kB 的 L2 缓存,包含 4 MB 的多核共享存储器,每个内核频率最高可达 1.4 GHz,在具备高处理速度的同时能够在芯片内部完成多个内核并行操作,能够大大提高运算速度,为快速实现多路信号参数测量提供了良好的硬件平台[1]。

# 1 软件设计基础

# 1.1 信号参数测量工作原理

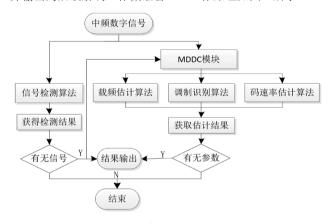

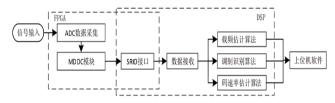

信号参数测量主要由信号检测算法、载频估计算法、调制识别算法和码速率估计算法组成,测量参数包括频率、带宽、信噪比、调制类型、码速率等。其工作原理为: (1)信号检测算法完成信号粗检测估计,获得宽带内多个信号的中心频率、带宽、信噪比等检测结果,并输出参数; (2)多路数字下变频(multichannel digital down conversion,MDDC)模块利用信号检测算法估计出来的参数对宽带内多个信号进行分离,并完成数字下变频、滤波、抽取等处理; (3)载频

1. 中国电子科技集团公司第三十研究所 四川成都 610041

估计算法利用 MDDC 后的近似基带信号做进一步的频偏估计,得到更加精确的中心频率,并输出参数;(4)调制识别算法利用频偏估计后的基带信号进行调制样式识别,得到信号的调制类型,并输出为后续解调工作做准备;(5)码速率估计算法利用基带信号进行码速率估计,得到信号的码速率,并输出为后续解调工作做准备<sup>[2]</sup>。工作原理如图 1 所示。

图 1 信号参数测量工作原理

# 1.2 信号参数测量核心算法

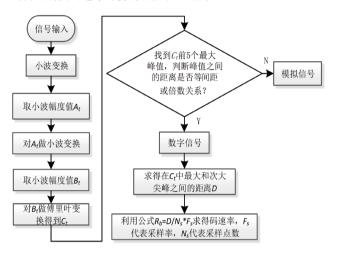

信号检测算法主要有能量检测法、相关函数检测法、高阶累积量检测法、循环谱检测法等<sup>[3]</sup>。本文采用频域能量检测法,首先利用 FFT 运算将信号转换到频域,再进行能量积累,将其聚集在信号载频附近,然后通过门限判定信号的中心频率及带宽等参数<sup>[4]</sup>,其工作原理如图 2 所示。

图 2 频域能量检测法工作原理

调制识别方法主要分为两类:基于似然比判决理论识别方法和基于特征提取的统计模式识别方法。前者计算量大,算法复杂,不易实现。本文采用了信号时频特征和小波变换相结合的识别方法,并综合考虑数模调制识别与码速率估计在计算方法上的相近之处,首先利用小波变换在提取瞬时变化信息的优势,可将模拟和数字信号进行分离,同时计算得到数字信号的码速率,然后分别对模拟信号和数字信号进行识别,以达到降低判决树级数、减少计算量的效果<sup>[5]</sup>,数模调制识别及码速率计算方法如图 3 所示。

图 3 数模调制识别及码速率计算方法

#### 1.3 信号参数测量软件运行环境

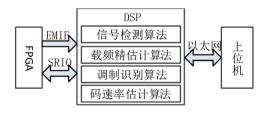

软件基于 FPGA+DSP+ 上位机软件的设计架构, DSP 芯片采用 TMS320C6678, DSP 与 FPGA 之间采用 SRIO 和 EMIF 接口通信, DSP 与上位机之间采用以太网接口通信, 信号参数测量软件运行在 DSP 上, 如图 4 所示。

图 4 软件运行环境

#### 2 软件设计与实现

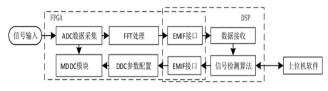

## 2.1 软件方案设计

DSP 软件设计主要分为两个任务:基于中频信号的信号 检测任务和基于基带信号的参数测量任务。为减少 DSP 的 计算压力,将信号检测算法中的 FFT 计算由 FPGA 完成, DSP 完成 FFT 计算后的信号判决及参数估算工作,同时结 合 FPGA 在多路并行数字下变频方面的处理优势,为减轻高 采样率下数据接口传输压力和为提高接口的传输效率,将信 号参数测量任务前的 MDDC 模块设计在 FPGA 上,DSP 可 对 MDDC 模块进行参数配置 <sup>[6]</sup>。因此,信号检测任务设计流程如图 5 所示,FPGA 控制模数转换器(analog to digital converter,ADC)对中频信号进行采集得到数字信号并完成FFT 计算,将 FFT 计算结果通过 EMIF 接口传给 DSP,DSP 完成信号检测并将检测的频率、带宽等结果上报上位机软件,上位机软件动态维护信号检测结果队列,并将重点关注信号的参数下发到 DSP 信号检测算法模块,信号检测算法模块更新自身分析列表,并通过 EMIF 接口配置 FPGA 的 MDDC 模块,MDDC 模块根据配置参数完成下变频、滤波和抽取得到基带数据 <sup>[7]</sup>。信号参数测量任务设计流程如图 6 所示,首先FPGA 将 MDDC 后的基带数据通过 SRIO 传给 DSP,DSP 根据上位机指令完成相应的参数估计,包括载频估计、调制类型识别、码速率估计,DSP将参数测量结果与分析列表融合后,将结果上报给上位机软件,上位机软件动态融合信号检测结果与信号参数测量结果到显示列表中。

图 5 信号检测任务工作流程

图 6 信号参数测量任务工作流程

#### 2.2 软件并行结构设计

多核 DSP 内核控制模型有两种:主从模型和数据流模型。主从模型是选择一个核作为主核,其它核作为从核,主核负责分配任务给从核执行,这种应用场景要求各个从核运行的任务独立,不需要进行同步和数据交互。数据流模型也叫串行工作模型,它将一个计算任务分为多个步骤,每个步骤分配到不同的核,每个核执行处理后,将处理结果传递到下一个核继续处理,共同完成整个计算过程<sup>[8]</sup>。

在信号参数测量软件中,信号检测任务是产生信号参数测量任务的前提,它可通过控制 FPGA 的 MDDC 模块,产生不同的测量任务,分配给信号参数测量模块执行。而不同信道的信号参数测量任务是完全相互独立的,不涉及任务间同步与数据交互,而并行执行又需要建立在不同的信号处理单元上,因此,本软件并行设计适合采用主从控制模型,Core0 作为主核执行信号检测任务,Core1 ~ Core7 作为从核可独立执行程序相同的信号参数测量任务。多核配置在.cfg文件中通过 MultiProc 组件配置,本设计配置如下:

var nameList = ["CORE0", "CORE1", "CORE2", "CORE3", "CORE4", "CORE5", "CORE6", "CORE7"];

var MultiProc = xdc.useModule('ti.sdo.utils.MultiProc');

MultiProc.numProcessors = 8;

MultiProc.setConfig(null, nameList);

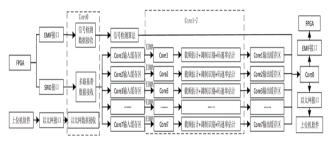

软件并行结构设计如图 7 所示。Core0 作为主核对外与FPGA 和上位机进行通信,对内负责与 Core1~7 通信,Core0 接收到多路基带数据后,根据从核空闲状态,填入空闲从核输入缓冲区,并通知从核执行处理任务,Core1 ~ Core7 没有参数测量任务时将一直空闲等待,对应从核接收到 Core0 的任务通知后从自己的输入缓冲区读取数据,执行参数测量任务,任务执行完成后将测量结果写入自己的输出缓冲区,并通知 Core0 任务处理完毕,进入空闲等待状态,等待下一轮任务;Core0 接到从核任务执行完成通知后,从对应从核的输出缓冲区读取结果,完成数据封装发给上位机软件。

图 7 信号参数测量软件并行结构设计

#### 2.3 核间数据通信方案设计

TMS320C6678 核间数据通信方式主要有:数据内存共享方式、基于 IPC 组件的消息队列(MessageQ)方式和基于多核导航器技术方式<sup>[9]</sup>。信号参数测量软件核间通信方面有如下需求,如表 1 所示。

表1 信号参数测量软件核间通信需求

| 消息通信           | 数据通信        |  |  |

|----------------|-------------|--|--|

| 主核通知从核执行参数测量任务 | 主核发送基带数据给从核 |  |  |

| 从核通知主核读取参数测量结果 | 从核发送测量结果给主核 |  |  |

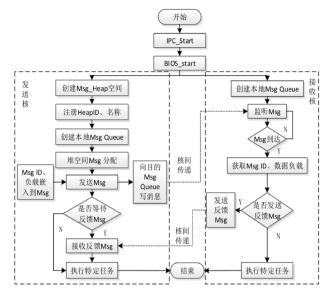

在消息通信方面,三种方式均满足要求,前面两种是基于 SYS/BIOS 实现的,而后者是一个硬件模块,从实时性操作系统维护性方面考虑,本文选取基于 SYS/BIOS 系统的 MessageQ 执行核间消息通信,其工作流程如图 8 所示。设计考虑超短波窄带信号,DDC 后采样率为 1 MHz,单通道基带数据长度为 8192,数据类型为 32 位 IQ 数据(高 16 位代表 I 路,低 1 位代表 Q 路),单次传输数据大小为 32 kB,同时从核需要大量缓存基带数据用于信号参数测量后的下一步处理(解调、解码等),因此采用数据内存共享方式,利用TMS320C6678 支持从 0x80000000 ~ 0xFFFFFFFF 最大 2 GB

DDR3 内存空间,在外部存储器 DDR3 上为不同从核分配足够的输入和输出缓存空间,用于主核和从核之间数据共享访问,防止数据的溢出和丢失 [10]。单核输入数据和输出数据缓存大小为 8192 字节,深度分别为 1000 和 100,DDR3 内存分配如表 2 所示。

图 8 MessageQ 的数据通信流程

表 2 DDR3 内存分配

| 起始地址       | 长度        | 大小     | 功能                      |

|------------|-----------|--------|-------------------------|

| 0x80000000 | 0x8000000 | 128 MB | Core0 程序所在区域,包含代码、堆栈等成分 |

| 0x88000000 | 0x8000000 | 128 MB | Corel 程序所在区域,包含代码、堆栈等成分 |

| •••        | •••       |        | •••                     |

| 0xB8000000 | 0x8000000 | 128 MB | Core7 程序所在区域,包含代码、堆栈等成分 |

| 0xC0000000 | 0x38000   | 224 kB | FPGA 的基带数据输入缓存区         |

| 0xC0230000 | 0x1F40000 | 31 MB  | Corel 基带数据输入缓存区         |

| 0xC2170000 | 0x1F40000 | 31 MB  | Core2 基带数据输入缓存区         |

| •••        | •••       |        | •••                     |

| 0xCBDB0000 | 0x1F40000 | 31 MB  | Core7 基带数据输入缓存区         |

| 0xCDCF0000 | 0x50000   | 320 kB | Corel 测量结果输出缓存区         |

| 0XCDD40000 | 0x50000   | 320 kB | Core2 测量结果输出缓存区         |

|            |           |        | •••                     |

| 0XCDED0000 | 0x50000   | 320 kB | Core7 测量结果输出缓存区         |

当主核进行了输入共享内存数据更新,从核需要使用 Cache 刷新函数,把数据刷新到 cache 中才能使用,同理当从核进行了输出共享内存数据更新,主核也需要进行刷新,osalCacheInv(void\* pBlockPtr, UINT32 byteCnt, BIT16 type, BOOL wait),第一个参数和第二个参数分别表示地址和长度。

## 2.4 核内多任务程序设计及优化

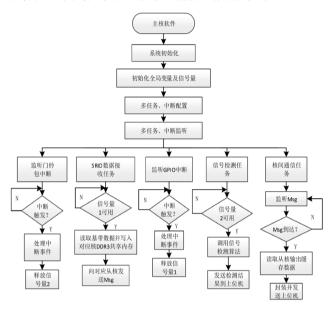

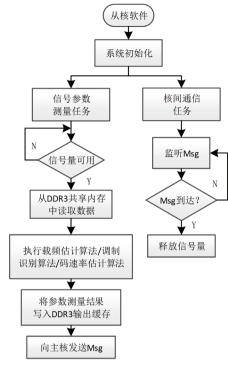

DSP 软件核内主要基于 SYS/BIOS 的多任务设计,任务 间通过信号量及优先级决定任务的运行次序。根据 2.2 节软 件并行设计方法,主核程序主要涉及三个任务和两个中断: SRIO 数据接收任务、信号检测任务、核间通信任务, GPIO 中断和门铃中断。如图 9 所示, 主核工作流程如下。

图 9 主核工作流程图

- (1) 主核启动后,首先根据.cfg 文件中相关内容配 置 SYS/BIOS,接着执行 main()函数,完成全局变量、信号 量、SRIO 数据接收任务(包含 SRIO 软硬件初始化)、信号 检测任务(包含 EMIF 初始化)和核间通信任务(包含 IPC MessageQ 初始化)、软硬件中断、以太网等初始化,然后 调用 BIOS start() 函数启动 SYG/BIOS 实时操作系统,监听 系统中的任务以及中断。任务创建初始化后, 先利用信号量 Semaphore pend() 函数使任务挂起, 当有外部触发到来时, 调用 Semaphore post() 函数释放信号量,任务执行。

- (2) 当 EMIF 数据到来时,产生 GPIO 硬件中断,释放 信号量 1, 信号检测任务获得执行权限, 从 EMIF 地址读取 信号检测数据,调用信号检测算法完成信号检测,并将检测 结果发给上位机软件。

- (3) 当 SRIO 数据到来时,产生门铃硬件中断,释放信 号量 2, SRIO 数据接收任务开始执行,从 FPGA 数据输入缓 存区读取数据并写入指定从核 DDR3 输入共享内存中,并发 送 Message 给指定从核。

- (4) 当接收到从核发送的 Message 后,核间通信任务 获得执行权限,从对应从核 DDR3 输出共享内存中读取结果 并封装发送给上位机。

从核程序主要涉及两个任务: 信号参数测量任务和核间 通信任务,如图 10 所示,从核主要工作流程如下。

图 10 从核工作流程

- (1) 从核启动后首先初始化运行环境,包括初始化全 局变量、信号量、信号参数测量任务、核间通信任务等初始化。

- (2) 监听 Message, 当主核 Message 到来时,释放信号 量,信号参数测量任务获得执行权限,从对应 DDR3 输入共 享内存中读取数据, 执行载波估计算法、调制识别算法和码 速率估计算法,处理完成后将参数测量结果放入 DDR3 输出 共享内存中,并向主核发送 Message。

C6678 芯片具有丰富的库函数,与本软件程序实现相关 的库函数主要有: DSPLIB(数字信号处理库)和MATHLIB(数 学库)。库函数是根据 TI 的汇编指令集进行手工汇编而成, 为用户程序执行效率远高于 C 语言,适用于实时性要求较高 的计算密集型信号处理。这些函数被封装到库文件中, 对外 不可见,调用库函数时,只需添加被调用库函数所在的路径, 并且在.c 文件的开始处包含所调用函数的头文件即可[11]。

如在载频估计算法、调制识别算法和码速率估计算法中 都会多次用到 FFT 计算,使用库函数:

DSPF sp fftSPxSP(int N, float \* ptr x, float \* ptr w, float \* ptr y,unsigned char\* brev,int n min,int offset,int n max)

其中 ptr w 和 brev 参数分别为旋转因子和蝶形算子,在 初始化时使用 void gen\_twiddle\_fft\_sp (float \*w, int n) 函数提 前计算好旋转因子存入 twiddles 数组中, 在初始化定义时就 设定好蝶形因子的值存入数组 Brev 中,这样可以提高效率, 避免反复计算。

在实现模拟信号AM和DSB信号区分、数字信号 MASK 与 MFSK 和 MPSK 信号间的调制识别中,会计算零 中心非弱信号段瞬时相位非线性分量的标准偏差  $\delta_{m}$ :

$$\delta_{dp} = \sqrt{\frac{1}{c}} \left[ \sum_{a_n(i) > a_t} \varphi_{NL}^2(i) \right] - \left[ \frac{1}{c} \sum_{a_n(i) > a_t} \varphi_{NL}(i) \right]^2$$

(1)

在计算 8192 点瞬时相位中可采用查表法,可以将正弦或余弦值计算出来,存入一张表中,在使用时将要求的数值转换为表中的位置,再根据位置取出数值即可,这样计算量大大降低,效率大幅上升。

除使用库函数提高执行效率之外,程序还用到了如下优化方法: (1) 用 Register 关键字定义高频次访问变量,减少CPU 读取时间; (2) 用 inline 声明高频次被调函数,节省函数调用的时间开销; (3) 优化条件判断顺序,减少无用判断带来的开销; (4) 开启编译器的优化选项,选择优化等级,提高执行效率 [11]。

# 3 性能测试及分析

## 3.1 试验环境

本信号参数测量软件在 CCS 5.3 编译环境下实现,硬件为现有项目信号处理板(1 片 V7+1 片 C6678 芯片)架构。信号中频输入 140 MHz,带宽 60 MHz,ADC 采样率200 MHz,信号检测 FFT 计算点数选为 16 384 点,基带数据采样率为 1 MHz,载频估计 FFT 计算点数 8192 点。MATLAB 生成 7 种调制样式的频域不混叠信号,相邻信号信道间隔 1.5 MHz,不同样式信号参数如表 3 所示。将生成的多信号波形文件加载到信号源(R&S -SMCV100B)中,设置信号源输出频率 140 MHz。

表 3 7 种调制样式信号参数特征

| 信号 | 载频 /MHz | 调制方式 | 码速率<br>/ (kbit·s <sup>-1</sup> ) | 3 dB 带宽<br>/kHz | 信噪比 |

|----|---------|------|----------------------------------|-----------------|-----|

| 1  | 140     | AM   | _                                | 1               | 13  |

| 2  | 141.5   | FM   | _                                | 15              | 16  |

| 3  | 143     | ASK  | 20                               | 20              | 12  |

| 4  | 144.5   | FSK  | 20                               | 40              | 13  |

| 5  | 146     | BPSK | 15                               | 20              | 17  |

| 6  | 147.5   | 4FSK | 10                               | 40              | 16  |

| 7  | 149     | QPSK | 15                               | 20              | 15  |

#### 3.2 信号参数测量测试

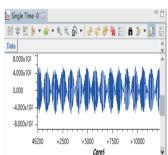

在 JTAG 调试环境下, Core0 读取 FPGA FFT 计算后的数据(110~170 MHz, 共 60 MHz/12.2 kHz=4917 个点), 平方求得功率并平滑滤波后通过 CCS 窗口的图形工具(Tools>Graph->Single Time)得到的检测前信号功率谱分布如图 11(a)所示, 从左到右依次为输入的 140 MHz、141.5 MHz、

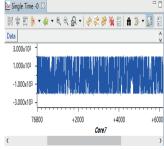

143 MHz、144.5 MHz、146 MHz、147.5 MHz、149 MHz 信号; Core1~7 执行 Core0 分配的信号参数测量任务读取到的基带波形如图 11(b~h)所示,依次为 AM、FM、ASK、FSK、BPSK、QPSK、4FSK 信号,检测得到的频率、信号带宽、信噪比以及参数测量结果在上位机软件列表显示如图 11(i)所示,由于载频估计 FFT 点数选择 8192,1 MHz 采样率下分辨率达到 122 Hz,因此载频估计和带宽误差均在很低的范围内,信噪比估计稍有偏差,可能和门限设置有关,调制识别和码速率估计均达到了较好的测量效果。

(a) CoreO 信号检测功率谱分布

(b) Corel AM 信号波形

Existing to Time -0 (3)

The state of the st

(c) Core2 FM 信号波形

(d) Core3 ASK 信号波形

(e) Core4 FSK 信号波形

(f) Core5 BPSK 信号波形

(g) Core6 QPSK 信号波形

(h) Core7 4FSK 信号波形

| 常规通信信号 |      |          |       |         |     |      |           |

|--------|------|----------|-------|---------|-----|------|-----------|

|        | 编号   | 频率(MHz)  | 方位(°) | 带宽(kHz) | 信噪比 | 调制类型 | 码速率(kbps) |

| 1      | 3001 | 140.0002 | 0.0°  | 1.2     | 13  | AM   |           |

| 2      | 3002 | 141.5004 | 0.0°  | 15.5    | 16  | FM   |           |

| 3      | 3003 | 143.0001 | 0.0°  | 20.4    | 12  | ASK  | 20        |

| 4      | 3004 | 144.5002 | 0.0°  | 50.1    | 12  | FSK  | 20        |

| 5      | 3005 | 146.0004 | 0.0°  | 20.2    | 17  | BPSK | 15        |

| 6      | 3006 | 147.5002 | 0.0°  | 50.5    | 15  | 4FSK | 10        |

| 7      | 3007 | 149.0006 | 0.0°  | 20.3    | 15  | QPSK | 15        |

(i) 信号测量结果上位机软件显示

图 11 CCS 中 Core 0~7信号显示与上位机软件显示结果对比

### 3.3 并行处理性能测试

为测试从核单核执行与多核并行执行加速比:  $S = T_1/T_n$ ,其中  $T_1$  表示单核执行时间, $T_n$  表示多核执行时间,测试中从核个数 n 分别取 1、2、4、7,通过加载不同数量的从核程序,测试在相同信号数量的条件下,不同从核数需要的处理时间,在 Core0 通过 toolTickRead() 函数读取发送消息时间 Tick<sub>0</sub> 和收到对应从核处理完成消息时间 Tick<sub>1</sub>, $\Delta t$ =(Tick<sub>1</sub>-Tick<sub>0</sub>) 即为单个信号参数测量所运行的时间, DSP时钟频率配置 1 GHz。由于从核加载程序完全一致,不考虑偶然误差带来的计算结果影响,统计结果如表 4 所示。

表 4 不同从核个数处理时间统计

| 从核个数     | 1           | 2          | 4          | 7          |

|----------|-------------|------------|------------|------------|

| 运行时间 /ns | 140 169 547 | 81 732 601 | 43 496 982 | 23 254 738 |

当从核个数分别为2、4、7时,加速比依次为1.7、3.2、6.1 倍。达不到理想加速比是因为实际的运算过程会由于核间通 信、数据传输等原因产生时间消耗和资源竞争,但相对单核 处理而言,处理性能还是得到了较大的提升。

#### 4 结语

本文主要研究了多路信号并行参数测量在 TMS320C6678 上的软件设计方法。根据信号参数测量软件算法的特点,进行了软件方案设计,选择了主从模式的内核模型、消息队列和数据内存共享的核间通信方案,并对核内多任务程序进行设计和编码优化。实验结果证明,该设计方法在满足功能要求的前提下,多核并行执行效率达到了单核的 6 倍,为进一步的解调解码实时性及宽带扩展需求奠定了基础。

# 参考文献:

[1] 张慧娟. 低功耗高性能多核 DSP 满足高性能计算 [J]. 电子设计技术,2012(2):16-19.

- [2] 周伟. 通信侦察信号处理的实现及其测试 [D]. 成都: 电子 科技大学,2016.

- [3] 郑华. 多信号分离及调制识别技术研究 [D]. 西安: 西安电子科技大学,2013.

- [4] 闫雪婷. 宽带通信信号频谱感知方法研究 [D]. 成都: 电子 科技大学,2018.

- [5] 王素霞. 无线通信系统中信号调制识别技术的研究 [D]. 成都: 电子科技大学, 2011.

- [6] 丁有源,汪安民.基于多核任务并行处理的 DSP 软硬件设计 [J]. 单片机与嵌入式系统应用,2012(5):43-45.

- [7] 王春芸. 基于多核 DSP 的信号分选软件设计与实现 [J]. 舰 船电子对抗,2018,41(6):112-115.

- [8] 郑武兴. 多核 DSP 并行处理的核间通信与编程技巧 [J]. 技术纵横, 2017(5):38-48.

- [9] 郑佳晶,李洪亮.基于多核 DSP 的核间通信方法研究 [J]. 电子工业专用设备,2023,52(2):64-71.

- [10] 周佩,周维超,王凯凯.TMS320C6678 多核 DSP 并行访问存储器性能的研究[J]. 微型机与应用,2014,33(13):20-24.

- [11] 李雪峰. 基于 C6678DSP 的雷达信号处理算法高效实现 [D]. 西安: 西安电子科技大学,2019.

# 【作者简介】

苏龙(1988—), 男, 陕西汉中人, 硕士, 工程师, 研究方向: 数字信号处理。

闫吉忠(1987—), 男, 山东枣庄人, 硕士, 工程师, 研究方向: 数字信号处理。

(收稿日期: 2024-04-11)