# 基于符号内延迟差分解调的 MSK 信号同步设计

唐佳乐<sup>1</sup> 张前南<sup>2</sup> 邓元俊<sup>2</sup> TANG Jiale ZHANG Qiannan DENG Yuanjun

# 摘要

针对最小频移键控(MSK)信号符号内延迟差分解调算法在解调前对信号同步的要求,以现场可编程门阵列(FPGA)为硬件平台,设计并实现了一种基于解卷绕差分相位相关的信号同步算法。同步算法从MSK基带相位变化和传输码元极性之间的相关特性入手,利用由周期同步码组成的通信数据帧头结构,将具有周期性的相位变化累加相关值进行分段叠加处理消除相关模糊,并提高信号同步稳定性后完成信号捕获和同步。计算机和硬件仿真结果表明,所提出的算法对频偏不敏感,在低信噪比条件下仍具有较高的性能,能满足大多数通信场景的应用需求。

关键词

MSK; 延迟差分解调; 码元同步; 相位相关; FPGA

doi: 10.3969/j.issn.1672-9528.2024.05.037

## 0 引言

最小频移键控(minimum shift keying,MSK)调制是一种特殊的连续相位频移键控(continuous phase frequency shift keying,CPFSK)调制,调制信号包络恒定、能量集中、抗干扰能力强。由于包络恒定,MSK 信号易于在非线性特性的信道中传输,受硬件系统中非线性器件影响小。同时,MSK 信号能量集中在 1.5 倍码元传输速率的带宽内,因此产生的带外干扰小,频带利用率高 [1]。诸多特点使得 MSK体制在卫星通信和军用通信等系统中得到了广泛的研究与应用。

常用的 MSK 解调方法包括相干解调、离散傅里叶变换解调、相位比较法、多符号检测法、差分检测法等<sup>[2]</sup>。其中,基于符号内延迟差分的 MSK 解调算法具有实现简单且对信号频偏和相移不敏感的特点。算法的抗频偏性能随传输码速率增加而提升,在解调时可以不用校正频偏与相移,适用于传输速率高、频偏范围大的 MSK 通信系统。但算法要想获得较高解调性能,则需要在解调前获取精确的码元同步<sup>[3]</sup>。

本文针对 MSK 符号内延迟差分解调算法对码元同步的 要求,以 FPGA 作为硬件实现平台,充分利用 MSK 基带信号相位变化与传输码元极性之间的相关特性,设计了一种 MSK 信号码元同步算法并进行了验证,算法具有抗噪声和多普勒频偏、实现复杂度低的优点。

# 1 解调和同步算法模型

# 1.1 符号内延迟差分解调

MSK 是调制指数 h=0.5 的 CPFSK,被看作是一种特殊的二进制频移键控(frequency shift keying,FSK)。码速率为  $R_b$  的 MSK 信号的两个载频偏移分别固定为  $\pm 1/4R_b$ ,因此 MSK 信号时域波形在码元变化时相位连续且不会发生跳变  $\{^{\{4\}}\}$ 。此时,信号波形的相关系数为  $\{0\}$ ,正好满足正交  $\{^{\{5\}}\}$ 。MSK 第  $\{k\}$  个码元信号波形可以表示为:

$$S_{k}(t) = \cos[2\pi (f_{c} + \frac{d_{k}}{4T_{s}})t + \varphi_{k}]$$

$$\varphi_{k} = \varphi_{k-1} - \frac{\pi}{2}(d_{k} - d_{k-1})k$$

(1)

式中:  $kT_s \le t \le (k+1)T_s$ ,  $T_s$  是码元周期,  $f_c$  是载波频率,  $T_s = R_b^{-1}$  是码元周期,  $d_k = \pm 1$  是第 k 个传输码元时刻的双极性码值,  $\varphi_k$  是第 k 个传输码元时间内的相位常数,保证在 kTs 时刻信号的满足码元转换时的 [6]。

令 MSK 信号初始相位  $\varphi_0$  为 0,化简后的 MSK 信号正交 表达式为:

$$S(t) = I_k \cos(\frac{\pi t}{2T_s})\cos\omega_c t - Q_k \sin(\frac{\pi t}{2T_s})\sin\omega_c t$$

$$I_k = \cos\varphi_k, Q_k = d_k \cos\varphi_k$$

(2)

式中:  $\omega_c=2\pi f_c$  是载波角频率, $I_k$  和  $Q_k$  可以看作原始序列  $d_k$  经过差分编码后持续时间为  $2T_c$  的码元序列。

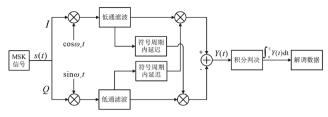

基于符号内延迟差分的 MSK 解调算法是一种利用 MSK 信号的差分特性在码元符号内进行延迟差分后通过积分判决 实现解调的方法。解调算法在积分判决时只依赖于当前码元 在符号周期内的差分信号,因此能够避免误码扩散且算法对 频偏和相移不敏感。解调算法实现框图如图 1 所示。

<sup>1.</sup> 哈尔滨工程大学 黑龙江哈尔滨 150001

<sup>2.</sup> 北京遥感设备研究所 北京 100000

图 1 MSK 解调原理框图

首先,在接收端用本振  $\cos \omega_c t + i \cdot \sin \omega_c t$  对 MSK 信号 S(t) 进行正交下变频得到下变频 IQ 信号,经过低通滤波后得到基带 IQ 信号  $^{[7]}$ 。将基带 IQ 信号以码元周期内采样点为单位延迟之后和原始基带 IQ 信号进行差分运算获得包含原始传输码元信息的信号 Y(t),通过在一个码元周期内对 Y(t) 进行积分运算和极性判决实现正确解调。

积分过程可以用多点叠加的方式表示为:

$$Y = Y(t) + Y(t + \Delta t) + Y(t + 2\Delta t) + \dots + Y(t + n\Delta t)$$

(3)

式中:  $\Delta t$  表示采样时间间隔,  $kT_s < t + n\Delta t < (k+1)T_s$ 。

$Y(t + n\Delta t)$  可以表示为:

$$Y(t + n\Delta t) = I(t + n\Delta t) \cdot Q(t + (n+1)\Delta t)$$

$$-Q(t + n\Delta t) \cdot I(t + (n+1)\Delta t)$$

(4)

选择适当的n和 $\Delta t$ ,通过如下极性映射即可实现解调。

$$d_k = \begin{cases} -1, Y > 0 \\ 1, Y < 0 \end{cases}$$

(5)

通过式(3)和式(4)可知,算法的解调性能受到每个码元周期内参与积分的采样点数量以及采样信号和原始码元之间采样偏移大小的影响。

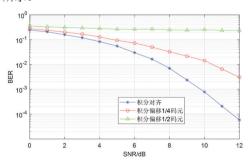

解调算法在不同积分采样点偏移条件下误码率仿真结果如图 2 所示。

图 2 算法在不同积分偏移条件下解调性能

由图 2 可以看出,随着积分判决解调时码元周期内数据 采样偏移的增大,误码率呈明显下降趋势。

# 1.2 MSK 基带相位分析

接收端下变频后的基带信号可以表示为:

$$S_{iq}(t) = I(t) + i \cdot Q(t) = I_k \cos(\frac{\pi t}{2T_i}) + i \cdot Q_k \sin(\frac{\pi t}{2T_i})$$

(6)

对基带 MSK 信号进行瞬时相位分析:由式(2)可知,通过 I(t)、Q(t) 求得的瞬时相位  $\theta(t_n)$  可表示为:

$$\theta(t_n) = \arctan(\frac{Q_t}{I_t}) = \arctan(\frac{Q_{k_n}}{I_{k_n}} \tan(\frac{\pi t_n}{2T_s}))$$

(7)

式中:  $t_n$  表示第n 个采样点时刻。第n 个采样点时刻相位值的一阶差分可以表示为:

$$\Delta\theta(n) = \theta(n) - \theta(n-1) = \theta(t_n) - \theta(t_n - \Delta t) \tag{8}$$

式中:初始值  $\Delta \theta(1)=0$ , $\Delta t$  表示采样时间间隔。

对差分后的瞬时相位按以下公式解卷绕:

$$\Delta\theta_{o}(n) = \begin{cases} \Delta\theta(n) & , |\Delta\theta(n)| \le \pi \\ \Delta\theta(n) - 2\pi, \Delta\theta(n) > \pi \\ \Delta\theta(n) + 2\pi, \Delta\theta(n) < -\pi \end{cases}$$

(9)

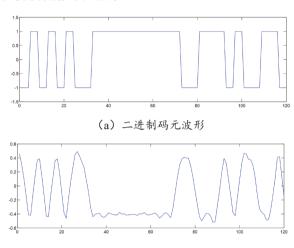

经过差分和解卷绕处理后的差分瞬时相位能够真实地反映 MSK 信号的瞬时相位变化趋势。由式(3)和式(8)可以看出,基带信号相位变化与码元周期  $T_s$  以及传输码元极性  $d_k$  具有相关特性 <sup>[8]</sup>。原始码元序列波形和接收端解卷绕差分相位波形分别如图 3 所示。

(b) 解卷绕差分相位波形

图 3 MSK 信号基带相位相关特性分析

由图 3 可以看出,每个码元周期内传输码元的极性和基 带信号瞬时相位的增减相对应。

#### 1.3 码元同步设计

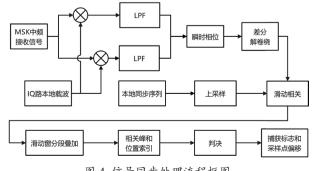

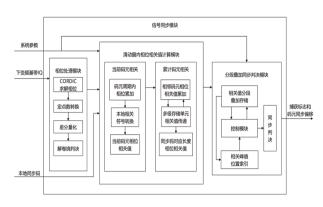

MSK 传输码元通常包含帧头和有效数据两部分,帧头通常由具有良好相关性的周期同步码组成。同步算法利用基带 IQ 信号解卷绕差分相位相关性和帧头中同步码的周期性,通过滑动相关、分组叠加和同步判决完成信号码元同步。算法完整的处理流程框图如图 4 所示。

图 4 信号同步处理流程框图

假设码元周期内采样点数为M,帧头中为周期的同步码 $P_o = \{P_1, P_2, \cdots P_N\}, P_i \in [-1,1]$ 。将长度为N的同步码进行M倍上采样后作为本地同步参考信号 $P_o(n)$ 与解卷绕差分相位信号 $\Delta \theta_o(n)$ 进行滑动相关。滑动窗口采样点大小为 $M\cdot N$ ,第n个采样点时刻在滑动窗口内解卷绕差分相位相关值可以表示为:

$$Z(n) = \sum_{m=0}^{M \cdot N - 1} P_o(M \cdot N - m) \cdot \Delta \theta_o(n - m)$$

(10)

由式(10)可知,当滑动窗口内采样数据和本地同步参考信号对齐时, Z(n)将出现对应相关峰,相关峰的峰值和在窗口内的位置索引可以作为信号同步的依据。

在信噪比较低或者同步码长度 N 较短的情况下,在接收信号的噪声和有效数据处可能会出现伪相关峰,从而影响后续信号同步判决,对此可以利用同步码的周期性对相关值进行处理。

由于同步码的周期性,接收信号解卷绕差分相位相关值 Z(n) 在帧头位置处会出现周期为滑动窗口大小的相关峰。根据窗口大小 $M\cdot N$  将相关值进行分段叠加处理 <sup>[9]</sup>。取分组叠加段数为 L,多段叠加后当前采样点时刻的解卷绕差分相位相关值可以表示为:

$$D(n) = \sum_{i=0}^{L-1} Z(n-i \cdot M \cdot N)$$

$$= \sum_{i=0}^{L-1} \sum_{m=0}^{M \cdot N-1} P_o(M \cdot N - m) \cdot \Delta \theta_o(n-i \cdot M \cdot N - m)$$

(11)

由式(11)可知,分段叠加处理后相关值的幅度近似提高了L倍。在帧头处,相关值将呈现出周期性的幅度增强。在噪声和有效数据处,由于Z(t)峰值的位置索引具有随机性,相关值幅度在增强的同时被多段平均,从而消除干扰。

根据同步参数选取合适的阈值对叠加相关值 D(t) 进行分析能够完成帧头信号的捕获,通过分析捕获到的相关峰峰值在滑动窗口内的位置索引 m 能够计算出当前码元信号的采样偏移,从而实现码元同步。

#### 2 同步算法计算机仿真分析

MSK 原始传输码元由周期的随机二进制同步码序列和随机二进制有效数据序列组成,经过差分编码、MSK 正交调制、信号叠加噪声、加随机长度信号时延等步骤,得到 MSK 中频接收信号对同步算法进行仿真分析,接收信号在时域可以看成由纯噪声段、帧头段、有效数据段组成。

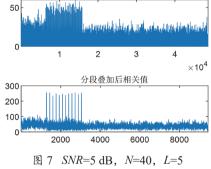

MSK 信号仿真参数如下: 码速率  $R_b$ =20 Mbit/s,采样频率  $f_s$ =80 MHz,多普勒频偏  $f_a$ =300 MHz,不同信噪比 SNR,同步码长度 N 和分组叠加段数 L 下相关值仿真结果如图  $5\sim7$  所示。由图 5 可以看出,在信噪比较高时相关值在帧头段明显区别于纯噪声段和有效数据段,经过分段叠加之后帧头段

相关峰特征更加稳定和明显。由图 6 可以看出,随着信噪比降低,伪相关峰数量大大增加。没有经过分段叠加的滑动相关值在纯噪声段和帧头段变得难以区分,经过分段叠加后相关峰的幅度相对降低,同时稳定性也受到了影响。由图 7 可知,在低信噪比下,增加同步码长度 N 和分组叠加段数 L 能够补偿信噪比降低带来的伪相关峰增加和不稳定问题。

以上仿真表明,同步算法对频偏不敏感,影响同步性能的参数主要是接收信号信噪比、同步序列长度和分段叠加段数。根据数据帧结构选取具有良好相关性的同步序列、调整叠加段数和同步序列长度,即使在更低信噪比下,仍能实现正确同步。

#### 3 硬件设计与实现

以 Vivado2018.3 为设计开发环境,Xilinx 的 Xc7z100 芯片为实现平台,设计并实现信号同步模块。同步模块由相位处理模块、相位相关值计算模块和分段叠加判决模块三个部分组成<sup>[10]</sup>。同步模块整体设计结构如图 8 所示。

图 8 硬件设计结构图

硬件设计工作过程如下。

第一步:相位处理模块接收正交下变频模块中产生的基带 IQ 信号通过 CORDIC 算法计算出瞬时相位,通过对定点小数表示的弧度制相位进行定点数转换和量化计算后完成相位差分和解卷绕。

第二步:在相位相关值计算模块中,分两步将解卷绕差分相位和本地同步码元进行滑动相关。首先按照码元周期内采样点数M对输入的解卷绕差分相位进行存储和累加得到当前码元周期对应的相位相关值;然后根据选取的本地同步码元极性 $P_i \in \{P_1, P_2, \cdots P_N\} \in [-1, 1]$ 和长度N对码元周期相位相关值进行符号转换来代替乘法运算,再通过在数组内依次对相乘后相关值进行累加、存储和多级传递的方式,获得滑动窗内的解卷绕差分相位相关值。

第三步:在分段叠加同步判决模块中,根据输入的叠加段数 L等参数通过状态机控制 RAM 读写对解卷绕差分相位相关值进行存储并标记位置索引后进行分段叠加。根据输入的阈值对分段叠加后多个相关值峰值和位置索引进行同步判决后,即可完成信号捕获和码元同步。

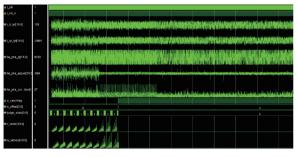

用仿真软件生成图 5 中仿真参数下中频 MSK 接收信号 进行硬件仿真测试,实现效果如图 9 所示。

图 9 同步算法整体仿真图

由图 9 的仿真结果中可以看出,经过正交下变频、相关运算后的解卷绕差分相位相关值 ila\_phs\_correlation 和图 5 中一致,经过分段叠加后相关值 w\_ramout 在帧头段特征明显。根据阈值和位置索引判决后在帧头段中间位置输出了信号捕获信号 o catchflag 和计算出的信号采样偏移 o offset,通过

对信号偏移进行补偿完成信号码元同步。

## 4 总结

本文针对符号内延迟差分解调算法对码元同步的要求,设计了一种MSK信号同步算法并完成了硬件实现。结果表明,通过选取合适的同步参数,算法能够在低信噪比和大多普勒频偏条件下实现 MSK 信号同步,满足大多数 MSK 通信场景的应用需求。同时,算法中利用二进制码元进行相关运算,具有实现简单、节省乘法器硬件资源等优点。

## 参考文献:

- [1] 蒋青, 吕翊. 最小移频键控信号的检测和误码性能分析 [J]. 信息技术,2003(12):38-40.

- [2]WU C, WANG S, ZHAO Y.A low complexity multi-symbol non-coherent msk receiver[C]//2019 IEEE 11th International Conference on Communication Software and Networks.Piscataway:IEEE,2019:133-139.

- [3] 张幼明, 贾建祥.MSK 信号的差分数字解调方法[J]. 舰船电子工程,2008(11):77-79.

- [4] 张辉, 代遵超. 一种改进的 MSK 信号解调算法 [J]. 通信技术, 2019,52(5):1061-1064.

- [5] 周帆, 冯川, 赵方昕. 数据链中 MSK 信号频率相干解调方 法仿真 [J]. 弹箭与制导学报, 2017, 37(5):115-118.

- [6] 颜利宏. 相干检测 MSK 信号的载波频偏估计和相位估计 算法研究 [D]. 长沙:湖南大学,2019.

- [7] 张楠,朱杰.MSK 调制直序扩频快速捕获算法的工程应用 [J]. 通信技术,2015,48(12):1348-1353.

- [8] 李壮壮.Link16 数据链调制解调关键技术研究及实现 [D]. 南京:南京理工大学,2022.

- [9]LIU Y, ZHANG T, XIA S, et al.A new rapid long pseudo-code acquisition algorithm in dsss signals[C]/2010 International Conference on Measuring Technology and Mechatronics Automation(ICMTMA 2010),v.1.Piscataway:IEEE,2010:196-199.

- [10] 徐芳, 梅晓, 李司. DSSS 接收机中 PN 码同步的 FPGA 实现 [J]. 现代电子技术, 2006(6):114-116.

#### 【作者简介】

唐佳乐(2000—), 男, 江苏无锡人, 硕士研究生, 研究方向: 无线通信。

张前南(1988—), 男,四川泸县人,硕士研究生,研究方向:数据链设计。

邓元俊(1996—), 男, 江西抚州人, 硕士研究生, 研究方向: 数据链总体设计。

(收稿日期: 2024-03-18)