# 一种基于 FPGA 的时序控制优化方法

禹 芳¹ YU Fang

## 摘要

同一种控制硬件模块处在项目不同层级中,外接设备待控制模块型号和数量各不相同,发挥不同的时序控制作用,且不同层级中的控制硬件模块对外所使用的 RS422 接口和光纤接口使用重合率基本上达到了 80% 以上,然而在 FPGA 这个硬件平台上做软件设计这块,涉及不同层级中的控制硬件模块管脚复用问题,很难在一个程序上实现所有的时序关系,进而要对不同的程序维护,这会增加很大的工作量。针对这个问题,提出一种在软件上统型设计的方法,不仅能防止人为固化程序出差错,还有利于后期维护。

### 关键词

时序控制; FPGA; 控制模块; 程序维护; 统型设计

doi: 10.3969/j.issn.1672-9528.2024.05.029

#### 0 引言

随着现在系统的集成度越来越高,处理速度也要求越来越快。现场可编程门阵列(field programmable gate array,FPGA)技术应运而生,FPGA<sup>[1-2]</sup>具有丰富的布线资源、可重复编程、集成度高及可并行处理等特点,受到广大设计者的欢迎。FPGA的输入输出引脚多,且配合上驱动控制芯片后,可灵活实现输入输出方向的控制选择以及输入输出的形式——差分或者单端。单端信号形式比如 TTL,可作为短距离传输,且它占用更少的低频连接器引脚,可在有限的空间内排布更多;差分信号比如 RS422<sup>[3-4]</sup>,它传输距离远,抗干扰能力强,传输速率高,可达兆比特级别,但占用连接器的空间是 TTL 的 2 倍。FPGA 的高速口速率可达到吉比特,在

1. 中国电子科技集团公司第三十八研究所 安徽合肥 230088

大数据传输时可很大程度上缩减时间,配合上光电转换模块, 有助于高速数据的长距离稳定传输。

基于以上特性,使用 FPGA 做主处理器,搭建控制模块硬件平台,是当前的设计主流。基于 FPGA 的硬件平台——控制模块,做时序处理<sup>[5]</sup>,不仅处理速度快,而且并行处理的特性完美解决了时序对齐问题。针对频点多、通道多的情况,需要进行高时效性的校正,用 FPGA 做处理完全契合。

赛灵思的 FPGA 资源包括可配置逻辑模块 CLB、DSP、嵌入块式 RAM 及时钟管理等。它不仅资源丰富,而且软件设计上使用的 vivado 软件平台,对于初学者来说,简单易上手。采用的硬件描述语言为 verilog 语言或者 VHDL 语言,verilog 语言类似于 C 语言,简单直接 [6-8]。

文章针对控制模块在某对抗项目中使用多个且发挥不同 作用的情况,提出一种在程序上做优化设计,减少程序版本 的方法。

- [6]KOEHN P, HOANG H, BIRCH A, et al.Moses: Open source toolkit for statistical machine translation[C]//Proceedings of the 45th Annual Meeting of the Association for Computational Linguistics: Companion Volume. Stroudsburg, PA: Association for Computational Linguistics, 2007:177-180.

- [7]LUO R, XU J, ZHANG Y, et al. Pkuseg: a toolkit for multi-domain chinese word segmentation[EB/OL].(2019-06-27)[2024-03-01].https://doi.org/10.48550/arXiv.1906.11455.

- [8]SENNRICH R, HADDOW B, BIRCH A.Neural machine translation of rare words with subword units[C]//54th Annual

- meeting of the Association for Computational Linguistics,vol. 3.long papers.Stroudsburg,PA:Association for Computational Linguistics, 2016: 1715-1725.

- [9] 李亚超, 江静, 加羊吉, 等.TIP-LAS: 一个开源的藏文分词词性标注系统 [J]. 中文信息学报, 2015, 29(6):203-207.

#### 【作者简介】

孙义栋(1997—), 男, 安徽马鞍山人, 硕士, 助教, 研究方向: 机器翻译。

(收稿日期: 2024-03-04)

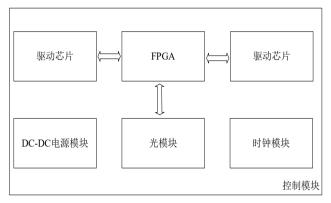

#### 1 系统组成

控制模块的硬件电路图主要是由 FPGA、DC-DC 电源模块、光模块、时钟模块以及驱动芯片组成,如图 1 所示。 FPGA 选用赛灵思 7 系列的 K7 芯片 XC7K325T,DC-DC 电源模块选用 LTM4644 芯片,光模块选用 TLZ850M 芯片,驱动芯片选用 SN74LVC16T245 芯片和 MAX1484 芯片,时钟模块选用 ADCLK954 芯片和 AD9516 芯片。

图 1 控制模块组成框图

XC7K325T 资源较多,满足一般控制需求,光模块 12 发 12 收,满足分发和收集状态信息的需求。

在某电子对抗项目中,阵面控制系统逻辑框图如下描述,总共有8个控制模块,待控制模块种类为7种。控制模块1~控制模块8为同一种控制模块,待控模块A~待控模块G为不同的待控制模块。物理上的布线方式包括以下几方面。

- (1) 控制模块 1 作为主控,分发数据和低频时序,其中大数据量的传输方式为:通过光纤接口接收外部传过来的数据以及将下一级和本身的状态收集通过光纤接口发送给外部。低频时序信号传输方式为:通过 RS422 接收外部的一些单比特数据,然后复制多份,分发给下一级。控制模块 1 将控制数据分发给控制模块 2 ~控制模块 8,控制模块 2 ~控制模块 8 将待控制模块 A ~待控制模块 G 的状态收集发送给控制模块 1。

- (2) 控制模块 2 在控制链路上:通过光纤接口接收控制模块 1 的控制数据以及通过 RS422 接口接收控制模块 1 的低频时序控制信号,进而控制模块 2 将数据解析下来通过 RS422 接口以同步串口 [9-10] 的通信方式来控制待控模块 A。控制模块 2 在状态收集链路上: 待控模块通过 RS422 接口以异步串口 [II-I2] 的通信方式将状态数据发送给控制模块 2,最后控制模块 2 将本身的状态以及待控模块 A 的状态通过光纤传送给控制模块 1。

- (3) 控制模块 3 在控制链路上: 通过光纤接口接收控制模块 1 的控制数据以及通过 RS422 接口接收控制模块 1 的

低频时序控制信号,进而控制模块 3 将数据解析下来通过 RS422 接口异步串口的通信方式来控制待控模块 B。控制模块 3 在状态收集链路上:待控模块通过 RS422 接口以单比特的通信方式将状态数据发送给控制模块 3,最后控制模块 3 将本身的状态以及待控模块 B 的状态通过光纤传送给控制模块 1。

- (4) 控制模块 4 在控制链路上:通过光纤接口接收控制模块 1 的控制数据以及通过 RS422 接口接收控制模块 1 的低频时序控制信号,进而控制模块 4 将数据解析下来通过光纤接口的通信方式来控制待控模块 C。控制模块 4 在状态收集链路上:待控模块 C 以光纤接口的通信方式将状态数据发送给控制模块 4,最后控制模块 4 将本身的状态以及待控模块 C 的状态通过光纤传送给控制模块 1。

- (5) 控制模块 5 在控制链路上:通过光纤接口接收控制模块 1 的控制数据以及通过 RS422 接口接收控制模块 1 的低频时序控制信号,进而控制模块 5 将数据解析下来通过光纤接口的通信方式来控制待控模块 D。控制模块 5 在状态收集链路上:待控模块 D通过 RS422 接口以同步串口的通信方式将状态数据发送给控制模块 5,最后控制模块 5 将本身的状态以及待控模块 D 的状态通过光纤传送给控制模块 1。

- (6) 控制模块 6 在控制链路上:通过光纤接口接收控制模块 1 的控制数据以及通过 RS422 接口接收控制模块 1 的低频时序控制信号,进而控制模块 6 将数据解析下来通过光纤接口的通信方式来控制待控模块 E。控制模块 6 在状态收集链路上:待控模块 E 通过 RS422 接口以异步串口的通信方式将状态数据发送给控制模块 6,最后控制模块 6 将本身的状态以及待控模块 E 的状态通过光纤传送给控制模块 1。

- (7)控制模块7在控制链路上:通过光纤接口接收控制模块1的控制数据以及通过RS422接口接收控制模块1的低频时序控制信号,进而控制模块7将数据解析下来通过RS422接口以异步串口的通信方式来控制待控模块F。控制模块7在状态收集链路上:待控模块F通过RS422接口以异步串口的通信方式将状态数据发送给控制模块7,最后控制模块7将本身的状态以及待控模块F的状态通过光纤传送给控制模块1。

- (8) 控制模块 8 在控制链路上:通过光纤接口接收控制模块 1 的控制数据以及通过 RS422 接口接收控制模块 1 的低频时序控制信号,进而控制模块 8 将数据解析下来通过 RS422 接口以同步串口的通信方式来控制待控模块 G。控制模块 7 在状态收集链路上:待控模块 G 通过 RS422 接口以同步串口的通信方式将状态数据发送给控制模块 8,最后控制

模块 8 将本身的状态以及待控模块 G 的状态通过光纤传送给控制模块 1。

控制模块  $2 \sim$  控制模块 8 作为从控制模块,互相独立,没有通信。待控模块  $A \sim$  待控制模块 G 作为待控模块,互相独立,也没有通信。

在工程项目的实际应用中,同时需要维护 8 个控制模块的程序,在程序版本的管理以及程序的固化上,都要做到不出差错。且在后续调试中,不同程序版本的控制模块硬件不具有互换性,不利于问题的排查和定位。

#### 2 方法的提出

#### 2.1 传统方法

在此项目中,总共有8个控制模块,上下级所连接的模块都不相同,所使用的硬件管脚都是一样的。由于不同的待控制模块功能不同,所使用的控制协议也不相同,在程序统一上有所限制。

传统方法上,控制模块1作为主控,接收控制模块2~控制模块8的控制数据,然后将数据分发给控制模块2~控制模块8,控制模块2~控制模块8接收各自的数据去控制待控模块A~待控模块G。在状态信息回传上,控制模块2~控制模块8收集待控模块A~待控模块G的状态信息,发送给控制模块1,控制模块1将这7包数据打包传送给上级,最终在界面显示。

针对以上在工程中常见的控制问题,可以在现有的硬件设计上,从软件层面出发,解决传统方法带来的不便利性。

#### 2.2 优化方法

首先将 8 个控制模块进行编号处理,分别编号为  $1 \sim 8$ ; 然后在软件接口协议里,定义一个控制模块编号字段,控制模块收到此命令后,就能区分出当前所在位置;最后根据控制模块编号分别去执行不同的功能。

工程中控制的光纤接口通信使用 FPGA 的高速口,媒介为光纤,采用 8 B/10 B 的编码方式,位宽为 16 bit,协议为自定义的裸协议;同步串口的通信媒介为差分低频电缆,位宽为各自待控模块内的控制长度,同步时钟速率为10 Mbit/s,上升沿放数据,下降沿采数据;异步串口的通信媒介为差分低频电缆,字节数为各自待控模块内的控制长度,波特率为 9600 bit/s,起始位为 0,停止位为 1。具体的实现方式如下。

(1) 定义软件接口协议,如表1所示。此方案采用如上的接口协议,字头用来判断接收的数据包,消息类型用来判断是控制指令还是状态指令,模块编号用来区分所在的模块位置,字尾用来判断数据包的结束标志。

表1接口协议

| 序号                                            | 内容              |

|-----------------------------------------------|-----------------|

| word1                                         | 字头 1            |

| word2                                         | 字头 2            |

| word3                                         | 字头3             |

| word4                                         | 消息类型            |

| word5                                         | 控制模块编号1~8       |

| word6-word[N <sub>1</sub> ]                   | 模块 2 控制内容或者状态信息 |

|                                               |                 |

| word[N <sub>6</sub> +1]-word[N <sub>7</sub> ] | 模块8控制内容或者状态信息   |

| word[N <sub>7</sub> +1]                       | 字尾 1            |

| word[N <sub>7</sub> +2]                       | 字尾 2            |

| word[N <sub>7</sub> +3]                       | 字尾3             |

| word[N <sub>7</sub> +4]                       | 字尾 4            |

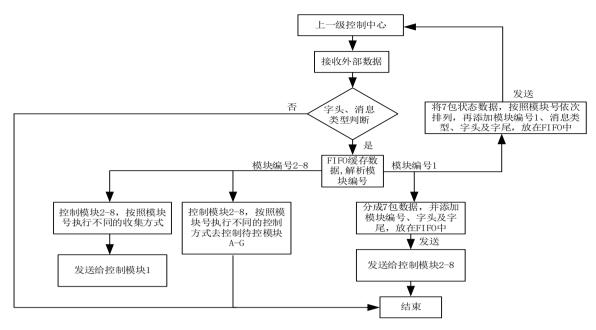

(2) 数据分包, 执行不同操作模块具体如图 2 所示。 控制模块1接收上一级控制中心传来的数据,数据格式是按 照表 1 的接口协议。操作方法是首先将接收的数据缓存下来, 连续判断字头1、字头2、字头3以及消息类型来判断是否 往 FPGA 的内存 fifo 里写,同时将控制模块的编号解析下来 作为该模块的编号,字尾1、字尾2、字尾3以及字尾4来作 为停止往内存 fifo 里写的标志。这样约定的好处是不用判断 数据包的长度,可适应不同的数据包,并且可作为一个通用 软件模块。如果该模块的编号是1,则执行拆包工作,将数 据分成7包,第1包数据主要组成为字头1、字头2、字头3、 消息类型、控制模块编号2、模块2控制内容、字尾1、字尾2、 字尾 3 以及字尾 4; 第 2 包数据主要组成为字头 1、字头 2、 字头3、消息类型、控制模块编号3、模块3控制内容、字尾1、 字尾 2、字尾 3 以及字尾 4; 第 3 包数据主要组成为字头 1、 字头2、字头3、消息类型、控制模块编号4、模块4控制内容、 字尾1、字尾2、字尾3以及字尾4;第4包数据主要组成为 字头 1、字头 2、字头 3、消息类型、控制模块编号 5、模块 5 控制内容、字尾1、字尾2、字尾3以及字尾4; 第5 包数 据主要组成为字头 1、字头 2、字头 3、消息类型、控制模块 编号6、模块6控制内容、字尾1、字尾2、字尾3以及字尾 4; 第6包数据主要组成为字头1、字头2、字头3、消息类型、 控制模块编号7、模块7控制内容、字尾1、字尾2、字尾3 以及字尾 4; 第7包数据主要组成为字头 1、字头 2、字头 3、 消息类型、控制模块编号8、模块8控制内容、字尾1、字尾2、 字尾3以及字尾4。如果该模块的编号是控制模块2~控制 模块 8, 则将数据解析下来, 按照待控模块的控制通信协议 执行不同的控制功能,来分别控制待控模块 A ~ 待控模块 G。 在状态收集上,控制模块2~控制模块8按照状态通信协议

图 2 数据分包流程框图

将待控模块 A ~待控模块 G 上报的状态收集打包通过光纤发送给控制模块 1,控制模块 1 将 7 包状态数据,按照模块号顺序依次排列,再添加字头 1、字头 2、字头 3、状态消息类型、控制模块编号 1、字尾 1、字尾 2、字尾 3 以及字尾 4 组成一包,通过光纤上报给上一级控制中心。

简而言之,在控制链路上,可以写一个大的控制逻辑模块,只是根据模块号来跳转执行不同的控制功能块。然而在状态收集上,必须先依赖控制指令里的模块编号,然后根据模块编号去执行不同的状态收集打包功能。低频时序控制也是根据模块编号去执行不同的收取或者分发,这样就可以保证在一个程序上执行控制模块2~控制模块8的功能。

(3) 仿真验证,通过 vivado 的行为仿真工具进行仿真,通过编写不同的模块编号数据,验证一个程序里的不同功能模块的正确性。

#### 3 结语

本文提出了一种多个控制模块在系统使用中,外接的待控模块不一致,而使用硬件管脚重合率很高的情况下,不同的控制模块在软件设计统型的优化方法,减少了在程序版本维护上的额外工作量,降低了后续的人为操作出错概率。本方法也存在一定的局限性,由于硬件资源的有限性,对控制模块和待控模块的数量有一定的上限要求。

#### 参考文献:

- [1] 杨海钢, 孙嘉斌, 王慰. FPGA 器件设计技术发展综述 [J]. 电子与信息学报, 2010(3):714-723.

- [2]KENNY J. 40 nm FPGA 给国防电子带来的优势和挑战 [J].

电子设计应用,2008(8):36-37+40-41.

- [3]RS-232、RS-422与RS-485标准及应用[EB/OL].(2011-03-29) [2024-02-12].http://www.360doc.com/content/11/1114/22/8137757\_164390616.shtml.

- [4] 段晓超, 段玲琳, 李化雷. 星型拓扑 RS422 信号传输特性 研究 [J]. 雷达科学与技术, 2016, 14(1): 91-94.

- [5] 褚兆文. 基于 FPGA 的雷达时序控制器设计与实现 [D]. 成都: 电子科技大学,2010.

- [6] 夏宇闻. Verilog 数字系统设计 [M]. 北京: 北京航天航空大学出版社,2003.

- [7] 吴继华. 设计与验证 Verilog HDL[M]. 北京: 人民邮电出版社, 2006.

- [8]MICHAEL D.Ciletti.Verilog HDL 高级数字设计 [M]. 北京: 电子工业出版社, 2007.

- [9] 王茹. 一种同步串口的设计与实现 [J]. 计算机技术与发展, 2008(2):173-176.

- [10] 詹必胜,吴斌方,杨光友. 多路同步串口的 FPGA 传输实现 [J]. 电子产品世界,2009,16(5):38-40.

- [11] 陈明正, 韦昌辉. 基于 Xilinx FPGA 平台的异步串口通信设计 [J]. 电脑知识与技术,2022,18(36):65-67+74.

- [12] 张继国. 一种利用 FPGA 实现串口通信的设计 [J] 电子世界, 2020(12):124-125.

#### 【作者简介】

禹芳(1990—), 女, 湖南衡阳人, 硕士, 工程师, 研究方向: 数字收发。

(收稿日期: 2024-03-13)