# 一种基于 FPGA 的宽带侦察系统脉冲数据采集的方法

王晨曦 <sup>1</sup> 杜旭华 <sup>1</sup> WANG Chenxi DU Xuhua

# 摘 要

在电子对抗领域中对雷达信号的脉内信息侦察识别是电子侦察情报系统必要的功能指标之一。电子对抗接收机为了能够侦察到所需信号一般需要增大接收瞬时带宽,脉冲信号采集将会产生海量数据。同时,所接收的信号是非合作信号,因而需要对接收信号需要进行检测与匹配。在 FPGA 上做海量数据的处理及信号的检测与匹配是目前宽带数字接收机比较常用的架构。目前,宽带侦察系统主要采用 PPC+FPGA 异构处理平台与 SRIO 互联技术。因此,提出了一种基于 FPGA 的宽带侦察系统脉冲数据采集方法。

关键词

侦察系统:海量数据:脉冲信号采集:异构处理平台

doi: 10.3969/j.issn.1672-9528.2024.05.014

#### 0 引言

当前宽带侦察系统中需要面对复杂的电磁环境, 尤其 是现在雷达系统为了降低截获概率、提高抗干扰能力、增加 相参得益,对雷达脉内信号进行了复杂的设计。侦察系统利 用传统特征构成脉冲描述字(pulse descriptor word, PDW) 对雷达信号特征进行表征已经无法识别当前多样化的信号类 型。因此,脉内特征分析是电子侦察系统中一项重要的功能 指标,脉内特征的提取可以为侦察信号的分选提供一个新的 维度。针对宽带侦察系统脉内分析的需求,需要设计一种脉 冲信号采集的装置。宽带侦察系统在频域、空域均是宽开系 统,需要处理海量数据。目前,宽带侦察系统的一种主流架 构是采用 PPC+FPGA 异构处理平台。为了满足 FPGA 与 PPC 之间海量数据传输需求,本文采用 SRIO 互联技术,能够满 足 FPGA 与 PPC 之间高速数据传输的需求。本文针对宽带侦 察系统设计了一种基于 FPGA 的脉冲数据采集装置, 该装置 结构简单、应用灵活、传输链路可靠, 能够满足现代宽带侦 察系统对脉内分析数据采集的需要。

# 1 宽带侦察系统架构介绍

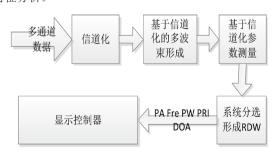

在电子对抗领域中,不同的侦察系统架构适用于不同的战术任务。基于信道化的宽带侦察系统,在侦察适应信号类型、提高侦察系统灵敏度、系统校正以及工程实现上具有很多优势。本文提出的脉冲信号采集技术适用于基于信道化的宽带数字波束侦察系统。基于信道化的宽带数字波束形成的侦察系统基本架构如图 1 所示。信道化模块利用多相滤波的算法完成前端宽带信号的子带划分,将宽带信号问题转换为

1. 中国电子科技集团公司第三十八研究所 安徽合肥 230000

窄带问题。基于信道化的多波束形成在空域中形成多个波束对空域进行瞬时覆盖。基于信道化参数测量模块完成单个脉冲的特征检测工作,对信号的 PA(幅度)、Fre(频率)、PW(脉宽)进行特征提取,该工作由于信号带宽大在 FPGA平台上进行实现。系统分选形成 RDW(radar description word),主要完成 PRI(脉冲重复周期)、DOA(波达方向估计)特征提取。该架构能够适应空域中多个目标,具有抗干扰能力强、可靠性高等优点。该侦察系统架构会提取出RDW 五大参数: PA、Fre、PW、PRI、DOA。本文在此侦察结果的基础上可以对指定目标进行脉冲数据的采集,用于脉内特征分析。

图 1 侦察系统基本架构示意图

#### 2 脉冲数据采集设计

## 2.1 脉冲数据采集架构

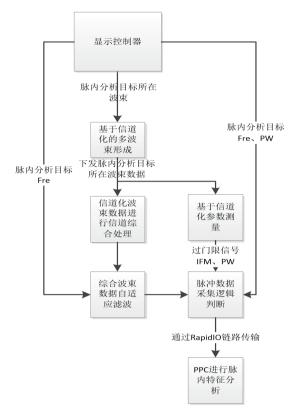

在系统硬件架构设计中,FPGA适用于海量数据的实时检测,PPC适用于复杂逻辑计算,脉内特征数据通过SRIO链路传输在PPC上进行特征分析。基于这种PPC+FPGA异构处理平台,脉冲数据采集流程示意图如图2所示。显示控制器选中侦察系统输出的目标进行脉内特征分析,此时显示控制器将目标所在波位指令下发给数字波束形成模块,将频

率信息下发给综合波束数字自适应滤波模块,将频率、脉宽 信息下发给脉冲数据采集逻辑判断模块。

图 2 脉冲采集流程示意图

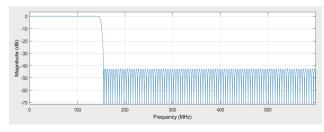

在图 2 中,信道化波束数据综合模块主要完成宽带样本的恢复。基于信道化的参数测量主要实时产生过门限信号、PW、Fre,用于后面的脉冲数据采集逻辑模块进行决策判断。本文在实际项目中侦察系统带宽为 1 GHz,采样率为 1.2 GHz 复采样,一个波束的数据率为 32 bit×1.2 GHz=38.4 Gbit/s,用到的 RapidIO 传输速率为 4×3.125 Gbit/s,在工程应用中除去协议开销稳定可靠的传输速率为4×3.125×50%=6.25 Gbit/s。根据应用需求侦察系统瞬时带宽信号一般都在 150 MHz 带宽之内,在不增加额外的硬件基础上完成脉冲数据采集的功能需要将宽带样本数据进行抽取滤波。因此,本文设计了综合波束数据自适应滤波模块,根据下发频点完成数据实时下变频滤波抽取,减少传输带宽。在 FPGA 中处理 1 GB 带宽数据主时钟采用 150 MHz,则需要 8 路数据并行处理,自适应滤波模块需要设计为 8 抽 1。利用 MATLAB 软件对 FIR 滤波器进行设计,FIR 滤波器设计如图 3 所示。

图 3 FIR 滤波器设计

#### 2.2 自适应滤波模块设计

综合波束数据自适应滤波模块能够对 1 GHz 瞬时带宽内 任意中心频率滤波输出 150 MHz 的带宽数据。该模块收到 显控计算器的控制信息,得到需要滤波的中心频率 Fre1,对 1 GHz 带宽的原始信号进行下变频处理,变频点为 Fre1,将 下变频之后的数据通过已设计好的 FIR 滤波器进行滤波处理, 对于滤波之后的数据进行上变频操作,变频点为 Fre1,通过 该种方法即完成了 1 GHz 带宽的信号滤波到 150 MHz 带宽的 信号。

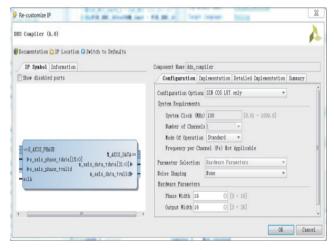

在综合波束数据自适应滤波模块中使用了数字上下变 频技术,该技术需要在FPGA内部产生8路并行点频信号, 产生该信号使用了多路并行 DDS (direct digital synthesizer) 技术。本文利用 Xilinx 提供的 DDS IP 核完成上述功能。 Xilinx 中 DDS IP 核实现数字频率值输入生成相应频率的数 字波形,其工作过程为:每来一个时钟脉冲clk,N位加法 器将频率控制数据 K 与累加寄存器输出的累加相位数据相 加,把相加后的结果送至累加寄存器的输入端。累加寄存器 将这个值作为取样地址送入 ROM, ROM 根据这个地址输 出相应的波形数据。结束相位累加器在基准时钟的作用下, 进行线性相位累加, 当相位累加器达到最大值时会产生溢 出,溢出一次即可认为完成了一个周期。对于1 GHz 带宽 的信号,系统采样率为复采 1.2 GHz, FPGA 会采用多路并 行的方式实现。本文中 FPGA 主时钟采为 150 MHz, 需要 8 路并行处理才能够完成 1 GHz 带宽信号的处理。假设系统 采样率为 Fs, FPGA 内部并行路数为 M 路, 需要产生频率 为 Fre1, DDS IP 核量化位宽为 N, 计算该频率对应的相位 控制字 Phase ctr, Phase ctr = Fre1/Fs×2<sup>N</sup>。本文单个 DDS IP核心配置如图 4 所示。

图 4 Xilinx DDS 核参数配置

FPGA 内部第M 路并行数据相位控制字累加值为 ddc\_fre i=Phase  $ctr \times M$ ,第M 路数据的相位初始值为 dds

phase=Phase\_ctr $\times$ M。根据上述原理,本文将核心代码相位控制字产生的方法列出,如图 5 所示。图 5 代码中,dds\_phase 是送给 DDS 核的相位控制字,ddc\_fre\_i 是产生点频的每个时钟下的相位累加量。

## always@(posedge clk sys) begin if(rst == 1)begin dds valid <= 0; dds phase[0] <= 0; dds phase[1] $\leftarrow$ 0; dds phase[2] <= 0; dds phase[3] $\leftarrow$ 0; dds\_phase[4] <= 0; dds phase[5] <= 0; dds phase[6] $\leftarrow$ 0; dds phase[7] <= 0; else begin dds valid <= 1; dds\_phase[0] <= dds\_phase[7] + ddc\_fre\_i</pre> dds phase[1] <= dds phase[7] + (ddc fre i<<1) dds phase[2] $\leftarrow$ dds phase[7] + (ddc fre i $\leftarrow$ 1) + ddc fre i dds\_phase[3] <= dds\_phase[7] + (ddc\_fre\_i<<2)</pre> dds phase[4] <= dds phase[7] + (ddc fre i<<2) + ddc fre i dds phase[5] $\leftarrow$ dds phase[7] + (ddc fre i $\leftarrow$ 2) +(ddc fre i $\leftarrow$ 1) dds phase[6] $\leftarrow$ dds phase[7] + (ddc fre i $\leftarrow$ <2) +(ddc fre i $\leftarrow$ <1) + ddc fre i dds phase[7] <= dds phase[7] + (ddc fre i<<<3) end

图 5 8 路并行 DDS 核心控制代码

## 2.3 数据采集逻辑控制模块设计

脉冲数据采集逻辑控制模块是本文中的核心模块。由于参数测量只有在脉冲信号的后沿才能给出PW信息,同时 fre 信息在脉冲后沿给出具有较高的精度,脉冲信号在

PW、Fre 这两个维度讲行筛选时, 需要先将讨门限信号讲行保存,在 脉冲下降沿进行决策判断保存的脉 冲信号是否满足判断条件。FPGA 芯片不适合大量保存数据, 因此过 门限保存的信号必须存储在外置 DDR 上。直接用 FPGA 控制 DDR 内存讲行数据的存储是一个比较复 杂繁琐的过程。本文提出了一种通 过 RapidIO 链路在 PPC 板卡上进行 数据存储的方式。经过前端自适应 滤波已经将数据带宽降低下来,单 路数据通过 RapidIO 链路能够满足 数据流水的传输, 因此可以满足脉 冲数据采集的传输。脉冲数据采集 流程如图 6 所示。

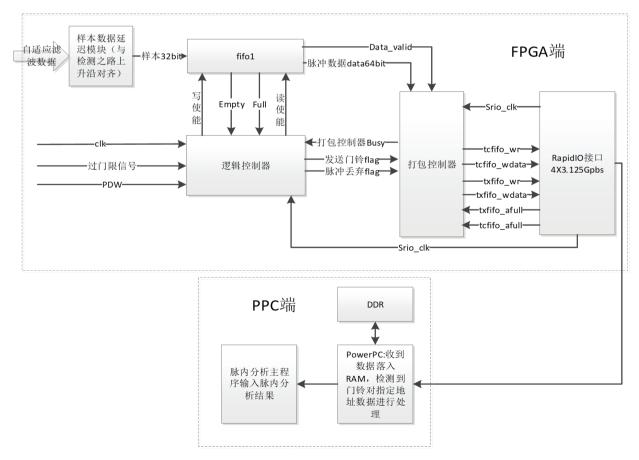

图 6 脉冲数据采集详细设计

宽带信号经过自适应滤波后会消耗时间资源,导致参数测量模块输出的过门限信号与滤波之后的信号在时间维度上不能够对齐。样本数据延迟模块就是将样本数据与参数测量过门限信号在时间维度上对齐处理。逻辑控制器主要产生样本数据的读写、过门限信号 PDW 筛选、发送门铃指令、脉冲丢弃指令。逻辑控制器中过门限信号是信道化参数测量输出检测过门限信号,PDW 是参数测量模块下降沿输出的PW、Fre、toa、PA 参数,发送门铃 flag 信号控制打包控制器向 PowerPC 发送门铃信号,脉冲丢弃信号逻辑控制器对脉冲下降沿对筛选条件进行判断,如果不满足筛选条件则发送丢弃信号。

打包控制器主要根据逻辑控制器的控制信号按照 RapidiIO 协议进行打包处理。打包控制里的 Busy 信号是根据 Rapid IO 接口产生的,该信号拉高时说明 Rapid IO 链路不能够正确接收数据,此时不能向 Rapid IO 接口发送数据。打包控制器收到发送门铃 flag 信号说明采集到的脉冲数据满足控制指令的要求,需要向 Rapid IO 接口发送门铃信息以通知 PowerPC 端取出脉冲数据进行数据分析。打包控制器收到脉冲丢弃 flag 信号说明此处采集获得的脉冲数据不能够满足控制指令的要求,此时的打包控制器需要将收到的 data64bit 数据丢弃处理。Rapid IO 接口采用 Xilinx 官方提供的 IP 核进行例化,配置的速率为 4×3.125 Gbit/s。

PowerPC 端在收到门铃信号后读取 DDR 指定地址数据,进行脉内数据分析。在 PowerPC 处理机制中,对门铃信息会进行中断响应。为了减少 PowerPC 门铃信息的响应,本文对FPGA 端发送门铃进行了设计,在逻辑控制模块中只有下降沿满足筛选条件后才发送门铃,无需每包 RapidIO 数据都发送一次门铃,这样就降低了 PowerPC 端的中断处理工作,提高了 PowerPC 端程序处理能力。

#### 3 结语

本文提出的一种基于 FPGA 的侦察系统脉冲数据采集的方法,能够应用于宽带电子侦察系统脉内分析的数据采集工作。本文介绍了当前宽带侦察系统一种主流的处理架构,并针对这种架构的特点设计了脉内分析的数据采集方法。其中设计的自适应滤波器能够在大瞬时带宽内根据显示控制指令对任意中心频率信号进行滤波并输出带宽 150 MHz 的信号,同时进行了抽取工作,有效降低了信号传输带宽,保证了脉内采集能够通过 RapidIO 链路传输。在自适应滤波器中,本文设计了 8 并行的点频信号,用于自适应滤波器的上下变频工作,该方法产生的上下变频信号的频率可以根据显示控制

指令任意设置。本文设计的数据采集逻辑控制模块结构清晰、模块划分明确,能够有效地产生脉冲数据采集的控制信号。数据采集逻辑控制模块的设计方法避免了FPGA端直接控制DDR方式,简化了FPGA逻辑控制,提高了项目开发效率。同时,该模块的设计使用了脉冲丢弃flag信号,减少了门铃的发送次数,降低了PowerPC端中断响应的开销,提高了PowerPC端程序运行效率。

因此,本文提出的基于 FPGA 的宽带侦察系统脉冲数据 采集的方法具有一定的工程实践价值。

# 参考文献:

- [1] 唐文武, 袁子乔. 基于 FPGA 的 SRIO 工程模块化提升设计 [J]. 火控雷达技术, 2021, 50(3):46-52.

- [2] 陈涛,郭立民,潘大鹏,等.被动雷达宽带数字接收机技术 [M]. 北京:电子工业出版社,2021.

- [3] 韩旭. 基于多路并行结构的宽带波形产生方案设计 [J]. 信息技术与信息化,2018(5):79-80.

- [4] 倪宣浩, 丛彦超, 武春飞. 基于多路并行 DDS 的快跳频信号发生器设计实现 [J]. 电子技术应用, 2018,44(11):94-98.

- [5] 杨东升. 雷达辐射源信号脉内调制方式识别研究 [D]. 哈尔滨: 哈尔滨工程大学,2021.

- [6] 米胜男. 雷达信号脉内调制类型识别研究与实现 [D]. 哈尔滨: 哈尔滨工程大学,2017.

- [7] 梁军,徐巍,舒汀,等.基于多路并行 DDS 的宽带雷达信号产生技术[J]. 现代雷达,2017,39(7):70-74.

- [8] 裴鑫,李健,段雪峰,等.超宽带脉冲星信号采集与处理 架构设计及功能验证[J].中国科学:物理学力学天文学, 2024,54(1):89-101.

- [9] 刘玄,田照星,郭庆庆.一种宽带信号采集分析设备的设计与实现[C]//第三十七届中国(天津)2023'IT、网络、信息技术、电子、仪器仪表创新学术会议论文集.天津:天津市电子学会,2023:3.

- [10] 张华翔, 杨伟娜, 马麟, 等. 宽带信号采集处理平台设计 [J]. 集成电路应用, 2022,39(12):4-7.

## 【作者简介】

王晨曦(1990—),男,安徽宿州人,硕士研究生,工程师,研究方向: 电子对抗。

(收稿日期: 2024-03-01)