# 基于 JFMK50T4-N 的数据处理模块的设计与实现

田欣园<sup>1</sup> 张 曼<sup>1</sup> 朱子恒<sup>1</sup> 刘 博<sup>1</sup>

TIAN Xinyuan ZHANG Man ZHU Ziheng LIU Bo

# 摘要

JFMK50T4-N 是一种 SRAM 型现场可编程门阵列器件,具有高性能、低功耗、小尺寸和低成本等特点。JFMK50T4-N 作为处理器的 PCIe 从设备,通过处理器的 PCIe 总线接口进行数据交互;利用 JFMK50T4-N 集成的 IP 核,完成从 PCIe 到 AXI 总线的转换; AXI 从接口模块产生 AXI 总线工作模式,UART IP 核、CAN IP 核和 Port 接口作为 AXI 的从设备,与系统中的 AXI 主接口互联,达到 IP 核与 AXI 总线之间的兼容,从而实现 RS422与 CAN 总线的接收与发送、心跳监控等功能。数据处理模块通过配置 DDR4、FLASH、以太网、串口等硬件资源,搭建嵌入式操作系统,实验验证了基于 JFMK50T4-N 设计的数据处理模块能够有效与外设进行信息交联。

关键词

IP核; FPGA; 硬件设计; 接口转换

doi: 10.3969/j.issn.1672-9528.2024.10.030

## 0 引言

由于半导体行业的进步,在单个芯片上集成复杂的系统成为可能,达到功率更低、成本更低、速度更高的板级设计<sup>[1]</sup>。片上系统(system-on-chip,SoC)有大量现成、可复用、各种总线接口的 IP 核存在<sup>[2]</sup>,具有高集成度、高可靠性和短研发周期特性<sup>[3]</sup>,且片上通信规范提供了一个标准接口,便于 IP 集成,并易于与 SoC 中的每个 IP 通信 <sup>[4]</sup>,因此广泛用于各种领域的嵌入式系统。

本文使用了一种能够执行AXI总线与UART、CAN、PCIe互联的SoC芯片——JFM-K50T4-N,其具备可编程功能,整合了功能强大、可按需配置组合的可编程资源,可支持实现输入输出接口、通用数字逻辑、存储器、数字信号处理等多种功能,可提供大量的专用时钟和布线资源,特别适合于完成复杂、高速的数据逻辑电路。JFMK50T4-N的封装为19mm×19mm,是一款小尺寸封装、低功耗和高性能的FPGA。

本文以JFMK50T4-N集成的IP硬核为基础,通过访问处理器电路、存储电路、以太网、RS232等硬件资源,设计了接口转换电路,实现了RS422、CAN总线等功能,并验证了基于JFMK50T4-N的数据处理模块能够有效与设备进行数据通信,并实现通用处理能力。

#### 1 模块架构概述

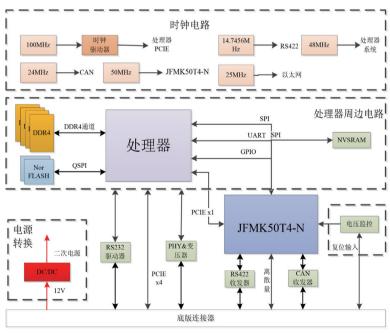

数据处理模块(DPM 模块)提供一个通用的综合硬件及软件的资源平台,包括 CAN、千兆以太网、RS422、RS232等接口,数据处理模块可作为信息传输、处理和管理中心,模块外形尺寸为 160 mm×100 mm<sup>[5]</sup>,满足 3U 结构要求。DPM 模块主要包括电源转换电路、时钟电路、复位电路、接口转换电路、处理器周边电路,模块的功能架构如图 1 所示。

图 1 数据处理模块功能架构图

<sup>1.</sup> 航空工业西安航空计算技术研究所 陕西西安 710065

#### 2 模块设计要点

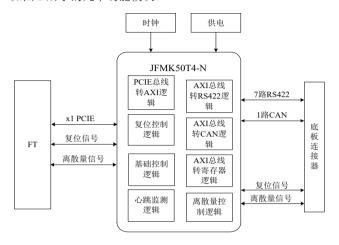

DPM 模块应用于计算机环境系统中,主要功能包括接口 转换、数据通信等。JFMK50T4-N的主要功能是产生不同接 口与上位机(处理器电路)间进行通信,其拓扑结构较为清晰, 不同接口间功能较独立。根据功能需求,将逻辑功能划分为 如图 2 所示的几个功能模块。

图 2 数据处理模块逻辑结构框图

## 2.1 总线转换功能模块

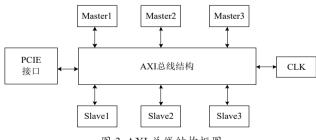

JFMK50T4-N 挂 载 在 模 块 内 部 PCIe 总 线 上, 作 为 PCIe 总线的从设备,处理器可以通过 PCIe 总线访问 JFMK50T4-N。JFMK50T4-N内部实现1路1线PCIe总线接口, 将 PCIe 总线转为 AXI 总线, AXI Interconnect IP 核提供多对 多的传输功能<sup>[6]</sup>。AXI总线系统可以看作三个部分: AXI主 接口、AXI 从接口和互联,信息可以在 AXI 主接口和 AXI 从接口之间双向传输, AXI4-Lite 接口适用于寄存器访问和数 据传输<sup>[7]</sup>, AXI 总线结构示意图如图 3 所示。

图 3 AXI 总线结构框图

## 2.2 RS422 接口电路设计

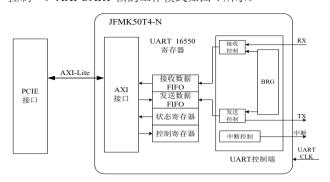

AXI UART IP 核可以分为三部分: (1) AXI 接口:实 现数据传输的接口: (2) 内部寄存器: 用于监控 IP 核在配 置状态下的工作状态; (3) UART 控制端: RX 控制、TX 控制、中断控制和 BRG。 BRG 生成所需的波特率对应的时钟, UART 通过 AXI 主接口收到的数据并串转换,从 RX 端接收 到的数据串并转换; RX 控制根据 BRG 采样得到并写入接 收数据 FIFO, TX 控制从发送数据 FIFO 中读取数据; 当接 收 FIFO 为"非空"或"空"时,中断控制触发,形成中断 控制<sup>[8]</sup>。AXI UART 核的工作模式如图 4 所示。

图 4 AXI 总线转 RS422 接口结构框图

数据处理模块配置7路RS422异步串行接口,由 JFMK50T4-N 内部实现7路RS422 TTL接口,JFMK50T4-N 的 UART 接口与 JFMK50T4-N 外部 RS-422 驱动器交联, JFMK50T4-N 内部通过对 7 路 UART 接口寄存器空间进行划 分,实现处理器对7路UART接口的独立访问,实现DPM 模块的 RS422 功能。JFMK50T4-N 实现对 RS-422 驱动器收 / 发数据使能的方向控制, JFMK50T4-N 控制 RS-422 驱动器 的接收/发送使能管脚,默认状态驱动器接收、发送使能管 脚均无效。

其协议芯片选具有内部驱动、接收和使能的接口芯片, 在使能端的控制下,将外部的逻辑信号通过驱动器转化为 差分信号, 由接收器中的比较器将接收的差分信号耦合到比 较器的输入端,利用比较器将差分信号转换为单端的逻辑电 平信号。RS422 支持 921 600 bit/s 的波特率,工作时钟采用 14.745 6 MHz, 通过连接器与板外信号交互, 实现对逻辑输 出串口数据的差分处理和差分信号接收转换。

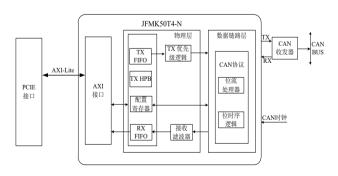

## 2.3 AXI 总线转 CAN 总线接口功能模块

AXI CAN 核用逻辑将 CAN 协议栈实现,其核心架构图 如图5所示。

图 5 AXI 总线转 CAN 接口架构框图

CAN 核分为物理层和数据链路层,物理层包含: (1) 接口功能: AXI接口与 CAN 控制器相连,进行信息交互; (2) 配置寄存器: 配置 CAN 控制器的工作状态。数据传 输层包括: (1)位时序逻辑: 监控 CAN 控制器与 CAN

总线的时序问题[9],并为位流处理器生成采样时钟; (2) 位流处理器:控制接收发送数据的序列发生器。

当 RX 数据经过数据链路层后,通过接收滤波器判断的 数据存储在 RX FIFO 中, AXI 接口通过配置寄存器读取缓存 区的数据: AXI 接口通过给配置寄存器设置发送指令,将数 据写入寄存器中,数据链路层对数据进行填充、校验[10],形 成TX数据,发送到收发器中。

DPM 模块实现了对 1 路 CAN 总线接口的控制器功能, JFMK50T4-N的 CAN 总线接口控制器与外部 CAN 驱动器 进行交联,实现了 CAN 接口功能。CAN 总线控制器应满足 CAN 总线协议,实现处理器对 CAN 总线接口的独立访问。 外接 3.3 V 的兼容 PHY 设备由 CAN 总线收发器芯片实现, 传输速率可达到 1 Mbit/s, CAN 工作时钟采用 24 MHz。

#### 2.4 AXI 总线转寄存器组功能模块

JFMK50T4-N 实现挂接在 AXI 总线下的控制寄存器组的 功能,控制寄存器组作为从设备,数据写入与数据读取操作 均由 JFMK50T4-N 发起。

控制寄存器组包含了中断状态寄存器、RS422 收发使能 控制寄存器、逻辑版本寄存器。其中,中断状态寄存器包含 RS422 和 CAN 总线中断, 只读; 逻辑版本寄存器包含版本 信息和时间信息,只读; RS422 收发使能控制寄存器实现7 路 RS-422 驱动器的接收 / 发送使能管脚, 可读、可写, 默认 状态驱动器接收、发送使能管脚均无效。

### 2.5 离散量控制功能

JFMK50T4-N实现DPM模块的输入/输出离散量的交联, 输入/输出离散量由模块底板连接器到处理器的互联,可以 实现 DPM 模块输入/输出离散量由模块底板连接器到处理器 的互联,输出离散量寄存器需在处理器未工作时输出离散量 对外输出低电平。

## 2.6 模块复位控制功能

FPGA 实现 DPM 模块各个部件间复位信号的交联,复 位信号包含手动复位信号、软复位、PCIe 复位。其中,手动 复位信号由底板连接器给到处理器,处理器输出 PCIe 复位信 号给 PCIe 从设备,处理器输出软复位给系统其他模块。

#### 2.7 模块基础控制功能

DPM 模块通过 JFMK50T4-N 对处理器实现: (1) 电源 上电控制:用于实现满足对处理器上电时序的控制;(2)复 位控制: 完成各种功能电路的复位控制, 保证处理器中所有 功能电路复位后处于正常的工作状态: (3)看门狗功能:由 FPGA 内部看门狗功能; (4) 中断控制: 根据 JFMK50T4-N 的各个不同供电的bank,提供1组1.8 V的I/O接口和4组3.3 V 的 I/O 接口,用于实现外部中断、离散量的输入。

## 2.8 心跳监控功能

JFMK50T4-N 应实现对处理器的心跳监测功能,用于控

制输出离散量寄存器,确保在处理器未工作时,输出离散量 对外输出保持低电平。

#### 3 处理器周边电路设计

DPM 模块采用高性能四核处理器, 其主频不低于 1.4 GHz, 单核计算能力不低于 4 GIPS。处理器周边电路包 括存储器电路和接口电路。

#### 3.1 存储器电路

处理器的存储器电路分为 DDR4 电路、Nor FLASH 电路 和 NvSRAM 电路。DDR4 电路采用 2 个 DDR4 控制器通道, 频率为600 MHz, 位宽72 bit (64 bit 数据+8 bitECC), 单个控制器设计采用 5 片 16 位的 DDR4L 颗粒组成 72 位, DDR 内存不低于 8 GB。

Nor FLASH 电路通过处理器的 QSPI接口, 挂接2 片 FLASH 芯片, 单片容量 256 MB, 最大传输速率可达 664 Mbit/s, DPM 模块的 Nor FLASH 存储容量为 512 MB, 为系统功能应用提供驻留和运行环境。

NvSRAM 电路利用处理器自身带有的 SPI 控制器,对 SPI 信号进行电平转换处理,与容量为128 kB的 NvSRAM 相接。NvSRAM 结合 SRAM 和非易失性存储技术,具有快 速的读写能力和断电情况下的数据保持能力。

#### 3.2 接口电路

处理器的接口电路可以分为: (1) PCIE 接口电路: PCIE 接口可分为 PEU0 和 PEU1, 可以集成 34 Lane PCI Express 3.0 接口, 2 个 x16 和 2 个 x1, 每个 x16 可分拆为 2 个 x8, 独立控制, 支持 root complex 和 endpoint。DPM 模块 配置了 2 路 x4, 2 路 x1 的 PCIe 端口, 其中 1 路 x1 PCIe 端 口与 JFMK50T4-N 相连; (2) 以太网接口电路: 处理器对 外提供一路 RGMII 以太网接口信号,通过 PHY 芯片转换为 UTP 信号, 经变压器对外输出一路 1000BASE-T 以太网信号; (3) 调试接口电路:处理器可集成 DUART 控制器,可对外 提供串口收发功能。DPM 模块使用 1 路 DUART 串口, 经电

平转换和 RS232 收发芯片,向底版连接器输出 RS232 信号。

#### 4 基础电路

## 4.1 电源转换电路

DPM 模块内部的工作电压包括: 5 V、3.3 V、2.5 V、 1.8 V、1.2 V、1.0 V、0.8 V、0.6 V。DPM 模块外部输入一路 独立 12 V 直流,板内选用 DC/DC 芯片变换为模块所需的 8 种电源电压,处理器和 FPGA 对上电顺序均有要求,分别通 过 FPGA 和 DC/DC 芯片的 TRACK/SS 信号控制。

## 4.2 时钟电路

在 DPM 模块的时钟电路设计中,通过 100 MHz 差分 时钟提供 FPGA 和处理器的 PCIe 接口工作时钟, DPM 模 块为所有 PCIe 设备提供 100 MHz 同源差分工作时钟,输 入电平为 HCSL 电平。RS422 接口、CAN 接口分别需要14.745 6 MHz 和 24 MHz 的时钟,FPGA 的 50 MHz 时钟由50M 时钟晶振提供,处理器的系统时钟 48 MHz 由 48M 时钟晶振提供,以太网 PHY、FPGA 芯片的 25 MHz 参考时钟由晶体提供。

#### 4.3 复位电路

DPM 模块的复位电路包括: (1) 电压监控: 监测 3.3 V 电压, 当输入电压小于 3.3 V, JFMK50T4-N 不加载逻辑, 处于不工作状态; 反之, JFMK50T4-N 正常加载逻辑; (2) 看门狗复位: 由逻辑实现看门狗定时器功能, 若看门狗定时器连续产生三次看门狗中断且均未得到处理时, 看门狗定时器发出看门狗复位, 处理器发出全局复位, 复位时间为 200 ms; (3) 手动复位: 当手动复位信号 MRST\* 置低时, 复位整个 DPM 模块。

## 5 模块功能验证

根据数据处理模块的功能,搭建功能测试环境,DPM 模块连接器与母板相连,以太网网口和 RS232 串口与 PC 机连接  $^{[11]}$ ,在固化 FPGA 逻辑、BOOT 软件、BIT 程序、模块支持层软件、驱动软件后,对 DPM 模块进行功能测试,具体分为以下几个测试项。

#### 5.1 基本功能测试

## (1) 电源电路测试

对模块电源转换电路的静态电阻进行阻值测试,确保阻值正常的情况,对模块进行 12 V 电压供电,测量 DC/DC 各个通道的输出电压数值是否正常,确保其在一定误差范围内,能让处理器、FPGA 以及其他芯片正常工作。

## (2) 时钟电路测试

使用示波器对模块时钟电路进行测试,具体为对各个晶振的时钟输出进行测量,观察其是否满足要求。

## (3) 复位电路测试

使用软件程序进行喂狗以及拨动手动复位开关,观察处理器是否会重新启动,以此来检查 DPM 模块的复位电路功能是否正常。

## 5.2 通信测试

采用两个 DPM 模块, DPM1 和 DPM2 进行 RS422 和 CAN 总线通信测试, DPM1 向 DPM2 发送数据, DPM2 收到 后将同样的数据再发送给 DPM1, DPM1 比对收到与发出的数据, 如数据一致,则 DPM 模块通信测试通过。

## 5.3 离散量测试

拨动输入离散量的拨动开关,读取 DPM 模块 FPGA 的内部寄存器数值,对输入离散量进行测试;对于输出离散量,向 JFMK50T4-N 内部寄存器中写数值,通过调试台信号灯,对输出离散量进行测试。

#### 5.4 小结

通过功能测试,处理器可以正常启动,且由JFMK50T4-N控制实现的RS422和CAN总线具备正常通信功能,模块之间可以进行信息交互传输。

## 6 总结

本文基于 JFMK50T4-N 实现了数据处理模块的设计,详细介绍了基于 JFMK50T4-N 的接口转换电路以及处理器周边电路的设计研究及实现。通过验证,本设计能够实现数据处理模块的基础功能,且能够实现数据处理模块之间的通信。

## 参考文献:

- [1]LI Z, LI J, ZHAO Y, et al.A SoC design and implementation of H.264 video encoding system based on FPGA[C]//2014 6th International Conference on Intelligent Human-Machine Systems and Cybernetics (IHMSC). Piscataway: IEEE, 2014: 321-324.

- [2] 胡景华. 基于 AXI 总线的 SoC 架构设计与分析 [D]. 上海: 上海交通大学, 2013.

- [3]JERRAYA A, WOLF W.Multiprocessor systems-on-chips[M]. New York: Springer New York,2007.

- [4]CHEN C, JU J, HUANG I.A synthesizable AXI protocol checker for SoC integration[C]//2010 International SoC Design Conference.Piscataway:IEEE,2010:103-106.

- [5] 韩强. 基于 VPX 标准 3U 通用处理模块设计 [J]. 电脑知识与技术, 2018,14(13):213+217.

- [6] 支点. 基于 AXI 总线的 PCIE 事务层设计与实现 [D]. 西安: 西安电子科技大学,2023.

- [7]MAHESH G, SAKTHIVEL S M. Verification IP for an AM-BA-AXI protocol using system verilog[J]. International journal of applied engineering research, 2017, 12:6534-6541.

- [8] 陆明远, 面向 AXI 总线的 UART IP 核设计 [D]. 西安: 西安电子科技大学,2017.

- [9] 季凤云. 基于 FPGA 的 CAN 总线控制器的研究与设计 [D]. 北京:北京交通大学,2019.

- [10] 吴宇伦. 基于 AXI 总线的 CAN 控制器设计与验证 [D]. 西安: 西安电子科技大学,2022.

- [11] 梁晓飞, 王爱林, 刘晓栋, 等. 基于 SM755 处理器的国产化处理模块设计 [J]. 电脑编程技巧与维护,2023(4):57-59+103.

## 【作者简介】

田欣园 (1998—), 女, 陕西西安人, 硕士, 助理工程师, 研究方向: 硬件设计。

(收稿日期: 2024-07-05)