# 基于 Chiplet 架构的国产芯片上电时序设计

潘志浩1 王 宇1 魏江杰1 PAN Zhihao WANG Yu WEI Jiangjie

#### 摘 要

论述了基于 Chiplet 架构的国产芯片上电时序的设计和验证。所使用的 Chiplet 芯片, 集成了国产处理器 及国产 FPGA, 并以此为核心设计出板卡。而电源的上电顺序影响着高速复杂板卡能否正常工作。严格 的上电顺序能够避免设计板卡各功能器件被损坏,也能使设计板卡正常进入工作状态。由于 Chiplet 架 构的复杂性,通过 CPLD 对整板电源进行控制,保证上电时序的精确与可靠。经 Modelsim 仿真实验和 实际上板验证,上电时序设计较为灵活可靠,可对设计板卡上各模块电源上电顺序进行有效控制,保证 复杂板卡的工作稳定性。

关键词

Chiplet; 复杂板卡; 上电时序; CPLD

doi: 10.3969/j.issn.1672-9528.2024.11.022

#### 0 引言

Chiplet 技术 [1-2] 是将一个功能丰富且面积较大的芯片裸 片(die)拆分成多个芯粒(Chiplet),并将这些具有特定功 能的芯粒通过先进封装[3-4]的形式组合在一起,最终形成一 个系统芯片。

本文为实现不同片间的异构通信,使用 Chiplet 技术将国 产处理器和国产 FPGA 通过先进工艺封装在一起,在整芯内 部进行片间互联,并以此为核心设计了一块复杂板卡。

然而良好的电源上电时序是整个设计板能够正常运行 的基础, 如何精确控制上电顺序和上电间隔至关重要。文 献[5]使用单片机来控制各路电源的上电并监测电压电流, 该设计对于小系统而言简单、可靠; 文献 [6] 采用了时序控 制芯片 UCD90160, 通过控制 GPIO 管脚来控制电源芯片的 使能信号,并根据整个系统时序要求配置各路电源的上电 时间间隔; 文献 [7] 基于 FPGA+DSP 架构,通过 FPGA来 控制整个系统的上电时序,上电即可使整个系统正常工作, 实现了状态机控制的上电时序及硬件短路保护功能。本文针 对基于 Chiplet 架构的国产芯片设计板卡 [8],设计了一种灵 活可控的上电时序<sup>[9-12]</sup>,使用 Lattice 的 CPLD 来控制板卡上 各路电源的上电顺序,并通过与 Modelsim 软件的联合仿真 和实际示波器测量来验证上电时序的正确性和可靠性。

#### 1 板卡设计

#### 1.1 硬件架构

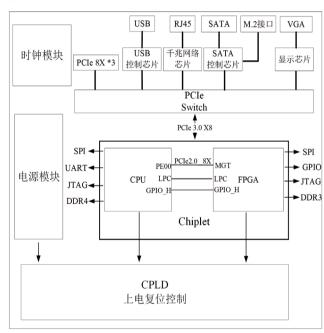

本文的设计板卡,采用 Chiplet 架构,将国产处理器和国

1. 中电科申泰信息科技有限公司 江苏无锡 214026

产 FPGA 进行封装,以 PCIe 为主要通信方式,内部进行互联。 板卡的设计方案如图 1 所示。

图 1 基于 Chiplet 架构板卡系统框图

由图 1 可知,除 Chiplet 芯片外,板卡还集成了 PCIe Switch 芯片、PCIe 外设、DDR 以及各低速外设接口。其中, CPLD 芯片由 ATX 电源 [13-14] 的 3.3 V 常备电供电,控制着板 卡所有受控电源的上下电顺序。相比于国内其余产品设计的 上电时序, Chiplet 架构的板卡整体较为复杂, 板卡集成的功 能外设较多,且对 Chiplet 芯片内部的 CPU 和 FPGA 上电顺 序及间隔有着明确的要求。若上电时序有误,则会损坏板卡 各功能器件,导致板卡无法正常进入工作状态。

# 1.2 CPLD 芯片

本文使用 Lattice 的 LCMXO2-2000HC 型 CPLD, 它是一款具有低功耗、低成本、快启动的可编程逻辑器件。该 CPLD 共分为 6 个 Bank, 不同 Bank 的 IO 电压可选,支持多种电平标准,如 LVCMOS、LVTTL、LVDS等,能够上电瞬时启动,迅速控制板卡中的各使能和反馈信号,满足板卡对信号精准控制的要求。

#### 2 上电时序设计

## 2.1 上电流程图

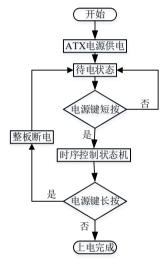

本文板卡的上电状态流程图如图 2 所示,ATX 电源给 CPLD 控制芯片提供 3.3 V 的常备电,使其能够控制板卡使能信号和反馈信号。设计板卡进入待电状态后,等待上电信号。当电源键被短按时,CPLD接收到上电信号(PS\_ON信号),进入时序控制状态机,控制各级信号,完成上电。若电源键被长按,则整板电源断电,重新进入待电状态。

图 2 板卡上电流程图

#### 2.2 信号控制

为保证板卡正常运行,按 Chiplet 芯片设计规范,各级电源需严格按照一定顺序完成上电操作。本文采用分步式上电方法,主要分为两部分: FPGA 模块上电和国产处理器模块上电。表 1 为 CPLD 控制的主要输入输出信号。

表 1 CPLD 输入输出信号

| 信号名          | 类型 | 信号说明         |  |

|--------------|----|--------------|--|

| C1k_32K      | Ι  | 时钟频率为 32 kHz |  |

| VCCINT_EN    | 0  | 内核电源电压使能信号   |  |

| VCCINT_PG    | Ι  | 内核电源电压使能完成信号 |  |

| VCCAUX_EN    | 0  | 辅助电源电压使能信号   |  |

| VCCAUX_PG    | I  | 辅助电源电压使能完成信号 |  |

| VCCAUX_IO_EN | 0  | 端口电压使能信号     |  |

表 1(续)

| 信号名            | 类型 | 信号说明                  |  |

|----------------|----|-----------------------|--|

| VCC_AUX_IO_PG  | I  | 端口电压使能完成信号            |  |

| VMGTAVCC_EN    | 0  | GTX 电压使能信号            |  |

| VMGTAVCC_PG    | I  | GTX 电压使能完成信号          |  |

| VMGTAVTT_EN    | 0  | GTX 电压使能信号            |  |

| VMGTAVTT_PG    | I  | GTX 电压使能完成信号          |  |

| VCC1V5_EN      | 0  |                       |  |

| VCC1V8_EN      | 0  | <br>  HR/HP IO 端口供电电压 |  |

| VCC2V5_EN      | 0  | IR/IR IV ἡ口供电电压       |  |

| VCC3V3_EN      | 0  |                       |  |

| VCC3V3_PG      | Ι  | I0 口电压使能完成信号          |  |

| DDR3_EN        | 0  | DDR 电压使能信号            |  |

| FPGA_ALL_PG*   | 0  | FPGA 使能均完成信号          |  |

| VDD1V8&2V5_EN* | 0  | 各外设电源使能信号             |  |

| VDD1V8&2V5_PG  | Ι  | 各外设电源使能完成信号           |  |

| VDD_IO_EN      | 0  | IO 端口电源使能信号           |  |

| VDD_IO_PG      | Ι  | IO 端口电源使能完成信号         |  |

| VDD_OV9_EN     | 0  | PCIe 设备电压使能信号         |  |

| VDD_0V9_PG     | Ι  | PCIe 设备电压使能完成信号       |  |

| VDD_1V2_EN*    | 0  | 显卡芯片电压使能信号            |  |

| VDD_0V8_EN*    | 0  | CPU 核电使能信号            |  |

| VDD_0V8_PG     | Ι  | CPU 核电使能完成信号          |  |

表 1 中可以看出,本文的设计板卡所需控制的电源信号较多,且需要严格按照表格顺序上下电,其中的某几个信号间的上电间隔亦有着严格的时间要求(注:要求上电间隔信号表格已做加"\*"处理)。

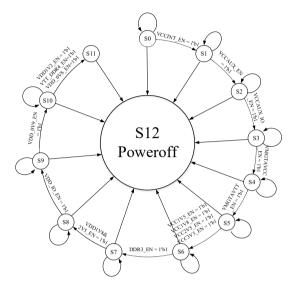

#### 2.3 控制状态机

相较于文献 [15-17] 简单系统的上电时序,本文板卡电源的上电时序较为复杂,如何有效地通过状态机控制 Chiplet 芯片的上电顺序和上电间隔至关重要。图 3 则为本文上电时序的控制状态机。由图 3 可知,在 SO 状态下,板间各路电源刚复位完成,处于待电状态;设计板卡的内核电压使能信号 VCCINT\_EN 默认为低,状态机持续进入在 SO 状态;当 CPLD 控制芯片接收到上电信号(PS\_ON)时,若当前Poweroff 信号未被拉高,则使能信号 VCCINT\_EN 被拉高时,状态机开始进入 S1 状态,FPGA 模块内核电源开始上电。电源芯片上电完成后,反馈的 PG(power good)信号输入 CPLD,表明 S1 状态已完成上电,CPLD 接收到反馈的 PG信号后,将下一状态 S2 的上电使能信号拉高,状态机随后进入 S2 状态准备上电。若每一状态反馈的 PG 信号持续为低,则表明当前状态尚未完成上电,状态机持续进入当前状态,等待 PG 信号被拉高。在进入 S7 状态后,为确保 FPGA 模块

的电源已全部上电完成,将 FPGA 模块所有 PG 信号做逻辑 "与"操作,得到FPGA ALL PG信号,表明FPGA模块所 有电压均已完成上电。并经过固定间隔时间使能 S8 状态使 能信号。在所有状态过程中, 若 Poweroff 信号被拉高,则状 态机立即进入 S12 状态, 板间电源所有的使能信号由高状态 变为低状态,设计板卡进入待电状态,等待重新上电。

图 3 上电时序控制状态机

#### 3 实验验证

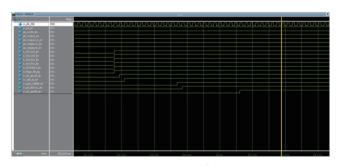

### 3.1 仿真验证

为验证本文的上电时序控制模块是否正确有效,对设 计的时序作 Modelsim 软件仿真。仿真结果如图 4、图 5 所示。

图 4 信号仿真图

图 5 局部放大仿真图

从图 4 可知,在上电信号 (PS ON)信号拉高后,状态 机由 S0 状态依次按顺序进入下一状态机, 分别拉高对应电 源模块的使能信号,各模块完成上电操作;由图5可知,在 Chiplet 芯片的 FPGA 部分电源上电完成后, FPGA ALL PG 信号由低变为高,经过固定间隔时间后,Chiplet 芯片的CPU 部分电源开始上电。在图 4 最后, Poweroff 信号被拉高, 状 态机进入 S12 状态, 所有使能信号由 1 变为 0, 符合本文的 时序设计。

# 3.2 板级验证

为验证本文设计时序在实际场景下的正确性,将逻辑 代码综合实现后生成的文件通过 JTAG 连线烧录进设计板 卡。由于本文控制的信号较多, 受篇幅限制, 在此列举其 中几个较为重要的信号,使用示波器进行测量记录。所测 信号如表 2 所示,测量结果如图 6 ~ 图 8 所示(注:示波 器不同通道所使用的电压幅值、间隔周期等信息于测量结 果图底部所示)。

表 2 示波器测量信号

| 序号  | 信号名                          | 水平刻度 | 垂直刻度 |

|-----|------------------------------|------|------|

| 第一组 | VCCINT_EN<br>VCCINT_PG       | ms   | 2 V  |

| 第二组 | VCCINT_PG<br>VCCAUX_EN       | ms   | 2 V  |

| 第三组 | VCC3V3_PG<br>DDR3_EN         | ms   | 2 V  |

| 第四组 | DDR3_EN<br>FPGA_ALL_PG       | ms   | 2 V  |

| 第五组 | FPGA_ALL_PG<br>VDD1V8&2V5_EN | μs   | 2 V  |

| 第六组 | VDD1V8&2V5_PG<br>VDD_IO_EN   | μs   | 2 V  |

| 第七组 | VDD_0V9_EN<br>VDD_1V2_EN     | μs   | 2 V  |

| 第八组 | VDD_1V2_EN<br>VDD_0V8_EN     | μs   | 2 V  |

图 6 第一、二组测量结果

图 7 第三、四组测量结果

图 8 第五、六组测量结果

图 9 第七、八组测量结果

图 6 (a) (b) 分别为表 2 中第一、二组测量结果;图 7 (a) (b) 分别为表 2 中第三、四组测量结果;图 8 (a) (b) 分别为表 2 中第五、六组测量结果,图 9 (a) (b) 分别为表 2 中第七、八组的测量结果。通过示波器所测信号可知,本文的设计板卡各级电源上电顺序和仿真结果相似,各级电源的使能信号拉高顺序均按表 1 顺序使能,完成了设计板卡的上电。

# 4 结论

本文基于 Chiplet 架构的国产芯片设计板卡使用 CPLD 设计了一种上电时序,并进行了验证。采用分步式上电的方法,先将 Chiplet 芯片的 FPGA 模块进行上电,经过固定间隔时间后再将 CPU 模块上电。仿真和实际测量结果表明了本文时序设计的复杂性和可靠性,能够满足设计板卡的上电时序要求。

#### 参考文献:

[1] 吴蝶. 先进封装 Chiplet 技术 [J]. 软件,2024,45(4):154-156+180.

- [2] 刘朝阳,任博琳,王则栋,等. Chiplet 技术发展与挑战 [J]. 集成电路与嵌入式系统, 2024, 24(2):10-22.

- [3] 马力,项敏,石磊,等.高端性能封装技术的某些特点与挑战[J]. 电子与封装,2023,23(3):90-98.

- [4] 赵瑾,于大全,秦飞.面向 Chiplet 集成的三维互连硅桥技术 [J]. 电子与封装, 2024, 24(6):1-13.

- [5] 张彪, 邢计元, 王帅. 板卡上电时序控制系统的设计和仿真 [J]. 网络安全与数据治理, 2023, 42(1):98-103.

- [6] 徐龑. 一种基于 OpenPower 平台的上电时序配置方法: CN201511007529.7[P]. 2016-05-25.

- [7] 黄伟,基于双核 DSP和 FPGA 的电力电子控制平台开发 [D]. 北京:北京交通大学,2016.

- [8] 郭旭, 陆晓峰, 潘志浩. 基于国产处理器的 Chiplet 原型系统设计与验证 [J]. 集成电路应用, 2023, 40(4):1-3.

- [9] 徐健, 吴海青, 包佳立, 等. 基于 CPLD 的交换机电源时序 研究 [J]. 电子设计工程, 2024, 32(5): 89-94.

- [10] 马茗岗, 罗永升, 孙尚, 等. 基于 CPLD 的多电源上电时序的控制设计 [J]. 电子世界, 2016(22): 56-57.

- [11] 冯景, 张繁. 基于可编程逻辑器件的电源上电时序控制 [J]. 中国集成电路, 2020, 29(12): 69-72.

- [12] 禹芳. 一种基于 FPGA 的时序控制优化方法 [J]. 信息技术与信息化,2024(5):132-135.

- [13] 闫书强. 认识计算机的动力之源 ATX 电源 (上)[J]. 大众硬件, 2008(8):92-94.

- [14] 闫书强 .ATX 电源 (下)认识计算机的动力之源 [J]. 大众 硬件, 2008(9):108-110.

- [15] 余海生. 一种开关电源的时序控制电路设计 [J]. 微电子学, 2014, 44(5):629-633.

- [16] 张恒浩, 付鹏, 梁伟. 一种用于微波系统的输入电压控制 电路 [J]. 微电子学, 2017, 47(3):363-366.

- [17] 李辉, 高宁, 丁光洲, 等. 基于 LM3881 的 FPGA 电源时序控制电路设计 [J]. 集成电路应用, 2023,40(6):38-40.

#### 【作者简介】

潘志浩(1994—), 男, 江苏宿迁人, 硕士, 工程师, 研究方向: 硬件设计、FPGA。

(收稿日期: 2024-07-23)