# 应用于 ICS PCIE Gen2 的扩频时钟模块电路

葛浩正<sup>1</sup> 韩国旋<sup>1</sup> 许培元<sup>1</sup> GE Haozheng HAN Guoxuan XU Peiyuan

## 摘 要

为了满足 ICS(internet connection sharing,因特网连接共享)PCIE Gen2 协议,可提供输入时钟信号给PC、PCIE 桥芯片以及以太网等芯片,利用时钟扩频技术的研究来减少系统的电磁干扰问题。基于应用于 ICS PCIE Gen2 协议的设计要求,通过采用 SMIC 0.18 µm 工艺设计传统锁相环结构,包括鉴频鉴相器、电荷泵、环路滤波器、环形振荡器、分频器以及相位插值器所设计的扩频时钟模块电路,实现了在满足指标 400 MHz 输出频率的基础上对扩频深度控制在 -5 ×10<sup>-3</sup> 以内,频谱峰值能量降低了 10.32 dB,输出相位噪声在 1 MHz 频偏下为 -107.378 dBc/Hz。未扩频模式下输出时钟的确定性抖动为 31.6 ps,周期间 RMS 抖动为 5.1 ps;进行扩频后,周期间 RMS 抖动为 8.6 ps,满足了 ICS PCIE Gen2 的协议要求。

关键词

ICS PCIE Gen2 协议;扩频时钟模块电路;电磁干扰;振荡器;相位插值器

doi: 10.3969/j.issn.1672-9528.2024.03.039

#### 0 引言

由于集成电路芯片设计产业的蓬勃发展、鳍式场效应晶体管技术的出现,芯片中器件的特征尺寸<sup>[1]</sup>已经降到了5 nm,芯片的集成化程度越来越高,集成电路设计的规模日益减小,大量的器件集聚在集成电路系统板,所以芯片中器件与器件之间的相互干扰变得越来越多,向外散布的辐射能量也愈来愈多,也因此电磁干扰(electromagnetic interference,EMI)<sup>[2]</sup>的问题也愈来愈被人们重视。芯片性能的优劣和生命周期都与电磁辐射有着重大的关联,故注意电磁辐射的干扰并降低其辐射能量在芯片的设计环节是至关重要的,降低EMI 也成为急需重视的问题。

由于干扰源、数据信号之间的相互作用,电磁干扰在信号传输中会使得辐射能量扩散,很大程度上降低数据信号或误码的质量。为适应消费电子产品市场对高性能的芯片产品追求,高速电路系统对数据的生成以及持续时间、抖动和其他的要求变得越来越重视,传统降低 EMI 的解决方案通常都是在电路上利用屏蔽技术(shielding),即在电路外多加一层接地金属,通过金属吸收导地的方式来降低 EMI 效应。这种技术虽然相当有效,但在实际运用中往往会增加电路板面积、重量以及成本,在现今电子产品追求轻薄短小的主流中,并不是一个合适的选择方案。因此,扩频时钟模块电路(spread spectrum clock generator,SSCG)[3] 应运而生,发挥了重要作用。扩频时钟模块电

1. 航空工业西安航空计算技术研究所 陕西西安 710065

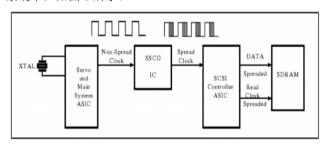

路采用将频谱能量进行扩展来控制辐射噪声,也因此降低了芯片本身和输出信号的电磁干扰程度,因此扩频时钟模块电路成为目前性能最好、成本最低的重要高速系统技术。为了应对电磁干扰,扩频技术被广泛应用在服务器硬盘机系统中,如图1所示。

图 1 硬盘机系统框图

本文基于应用于 ICS PCIE Gen2 协议的设计要求,使用传统锁相环结构,再结合片外的数字控制模块电路对相位插值器进行调相,进而对环形压控振荡器的输出进行调控,实现了频谱的能量扩展,达到了电磁干扰 EMI 的减小,实现扩频时钟模块电路的设计。

#### 1 扩频环路总体设计

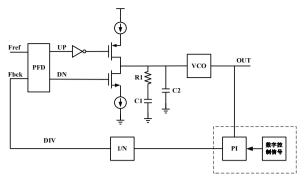

采用相位补偿的方法可以使扩频时钟模块电路的性能噪声和抖动都得到降低。故本设计采用相位补偿调制的技术,该系统在常规锁相环的基础上增加了相位插值器,并利用了数字控制模块对相位插值器尾电流源的控制,对环形压控振荡器的输出进行调制,实现了对时钟的扩频调制,扩频时钟模块电路的结构如图 2 所示。

图 2 扩频时钟模块电路

由图 2 扩频时钟模块电路的架构图可得到其架构主要由两个关键模块构成,第一个模块为锁相环结构,通过环路的工作后实现锁相环锁定,从而生成需要的时钟信号。另一个模块是扩频功能电路,由片外 FPGA 生成数字控制信号模块生成 31.2 kHz 的三角波控制相位插值器尾电流源开关,从而对压控振荡器的输出进行调相,进而产生调制扩频信号,完成对输出时钟的扩频。

## 2 电路结构

#### 2.1 鉴频鉴相器

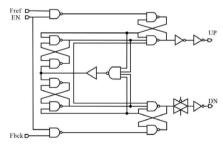

在扩频时钟模块电路中,PFD 的主要功能是从系统内检测外部输入信号  $f_{ref}$  和信号  $f_{bck}$  之间的频率差和相位差,将相位差变换为 UP 和 DN 信号的脉冲,以提供给后续的电荷泵。为了消除死区的影响,通过在鉴频鉴相器的复位路径上添加延时单元,当通过延时之后复位的输出脉宽可以打开后续电荷泵的充放电的开关时,死区的影响就会得到消除。

图 3 鉴频鉴相器电路设计

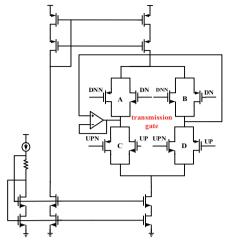

#### 2.2 电荷泵

电荷泵的功能是将其接收到的脉冲信号的转变为电流信号,从而为环路滤波器进行充电的操作。本设计使用的电荷泵如图 4 所示。在本设计共有 A、B、C、D 四个传输门开关的基础上,通过引用相反的信号控制开关来成为互补的开关,它们分别由 UP 和 UPN 信号,以及 DN 和 DNN 信号来实现控制,并用来减小时钟馈通的情况,其中 UPN 由 UP 信号反相产生,DNN 则由 DN 信号反相产生,当 UP 信号为高时,B 和 C 打开,Vetrl 电压增大。当 UP 信号为低时,A 和 D 打开,Vetrl 电压减小。其中加入运算放大器,并使用了对称的结构可以稳定 Vetrl 的值,电荷共享效应也得到了减小。

图 4 电荷泵结构图

#### 2.3 环形振荡器

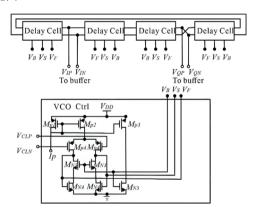

本设计将采用四路差分的环形振荡器 [4] 构成扩频时钟模块电路的重要模块。由于需对环路振荡器的延时单元尾电流源进行调控,故需设计出振荡器的控制单元生成振荡器的控制电压,以及四级差分环形振荡器的结构。本节设计的环形振荡器采用了插值法来进行改变延时,延迟单元的每一级电路由一个快路径和一个慢路径组成,由负载电阻  $R_d$  和差分输入管  $M_{N1}$  和下方的电流源  $V_{B1}$  和  $V_F$  构成快通路,由负载电阻  $R_d$  和差分管  $M_{N2}$ ,电流源  $V_{B1}$  和  $V_S$  以及增加电阻  $R_g$  和电容  $C_g$  构成慢通路,由左右快慢两个通路共同工作,从而实现控制振荡器的延时。图 5 为环形振荡器的四级差分总结构与控制单元图。

图 5 环形振荡器总结构图与控制单元图

如图 5 所示,本文设计使用了双端差动结构的振荡器,由于全差分运放为差分输入以及输出,输出的信号相位差为180°,由于差分结构能够很好地抑制输入共模信号的影响,故采用四级差分的结构来完成设计。其中  $M_{P1}$ 、  $M_{P2}$ 、  $M_{P3}$  为电流源, $V_{CLP}$  和  $V_{CLN}$  为两个  $M_{P4}$  的输入共模电压来控制下方电流源的电流,而  $M_{N3}$  和  $M_{N4}$  组成共源共栅电流源,生成相同的电压值  $V_B$ ,以及需要生成不同的电压  $V_S$ 、  $V_F$  来用于控制延时单元的尾电流源,从而控制延时单元的延时,改变环形振荡器的振荡频率。

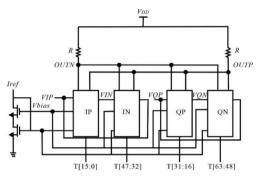

#### 2.4 相位插值器

本次扩频时钟模块电路使用相位插值器对传统锁相环进行扩频。由于相位插值器的非线性会严重影响扩频时钟模块电路性能,故设计了一款高线性度的相位插值器。本次设计的相位插值器结构图如图 6 所示。

图 6 相位插值器结构图

图 6 的相位插值器 <sup>[5]</sup> 由 IP、IN、QP 和 QN 四路共用电阻的差分对构成,每一个支路中的结构相同,以IP 支路为例,其中共有 16 个差分对管,每一个差分对都进行并联,其对管的开通与关闭是由其下方的电流源来进行控制,通过开关 T (15:0) 对每一个尾电流源进行控制,通过开关的控制来实现 IP 支路的电流输出,从而通过对四个支路的共同控制,实现各个支路的电流输出,再对支路的电流比进行计算,进而实现相位插值器的相位调节。为了使相位插值器尾电流的总电流值不变,且因为每个支路都存在 16 个开关控制总电流,故相位插值器每次在工作时,保证 64 个开关中只开通了 16 个开关,控制尾电流的大小。

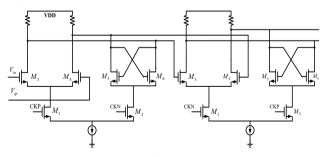

#### 2.5 分频器

在锁相环工作系统中,分频器的工作速度很是关键,高速二分频主要的设计分为源极耦合逻辑或者射极耦合(SCL或者 ECL)。如图 7 所示,本文设计了一款由两个锁存器构成的触发器的基于 SCL 逻辑的分频器,称之为电流模型主从锁存器。

图 7 高速二分频

高速二分频为一个模拟的分频器,由于本结构的使用原理与数字的相似,且其工作频率有着很大的优势,与器件的联系更强,差分信号噪声低的缘故,故采用此种分频器来对扩频时钟模块电路进行预分频,其结构由两个 CML to COMS的逻辑电路构成,包括了 12 个 MOS 管以及 4 个差分对,

每一个差分对的尾电流源分别作为 CKP 和 CKN 的控制端, OUTP 和 OUTN 作为分频器的输出端口,由输入时钟 CKP 和 CKN 控制信号的大小来对尾电流源控制,从而为差分对 输入稳点的电流,再通过负载形成输出。

#### 3 仿真结果分析

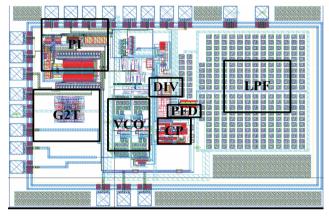

## 3.1 扩频时钟模块电路的主要版图

本文采用 SMIC  $0.18 \, \mu m$  的工艺,用 Cadence Layout XL 对扩频时钟模块电路主要模块电路的版图进行设计,图 8 为本次系统的扩频时钟模块的电路版图设计。其中版图包括了 6 个电源端口,以及 9 个信号端口,电源端口为 PAD\_VDD、PAD\_GND、AGND、DGND、DGND、DVDD。输出端口为 PFD 的  $F_{ref}$ 端,PI 的数字控制端 T<0-6>,以及两处偏置电压。该版图面积为  $1443 \, \mu m \times 980 \, \mu m$ 。

图 8 扩频时钟模块的版图设计

## 3.2 扩频时钟模块噪声与抖动

通过 Spectre 仿真器提取各个模块的版图参数,通过仿真得到各个模块的输出相位噪声后,使用 Matlab 软件通过各个模块对系统的输出噪声贡献公式并对其进行计算后拟合得到整个环路的输出噪声在 1 MHz 频偏下为 -107.378 dBc/Hz。

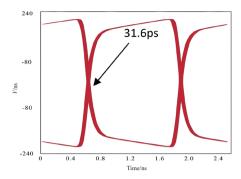

由于系统抖动会对整个环路的性能造成严重的影响<sup>[6-7]</sup>, 为测量未扩频时钟模块电路的确定性抖动、周期与周期之间 的抖动,以及扩频时钟模块电路的周期与周期间的抖动,眼 图是一种可以直观表示信号抖动性能的方式,由于其形状酷 似眼睛,故称之为眼图。

本节分别对扩频前与扩频后的电路使用后仿的网表进行了瞬态的仿真,通过 Eye Diagram 工具对扩频前的传统锁相环电路进行了眼图的仿真,结果如图 9 所示。图 9 显示的是未扩频前时钟模块电路的输出在环路锁定后 2.5 的眼图,可以清晰地看到眼图的存在,可以测量到未扩频时钟模块电路的确定性抖动为 31.6 ps,通过 Tool 的 Calculator 工具,通过Matlab 对环路的相噪分析,得到未扩频时钟模块电路的周期间 RMS 抖动为 5.1 ps。由于扩频后时钟模块电路的输出频率进行了展频,为一个三角变化的曲线,并不固定,可以看作

是系统电源引入的噪声,扩频后的眼图无法进行显示,对其周期间的 RMS 抖动进行计算可得为 8.6 ps。

图 9 未扩频时钟模块电路的眼图

## 3.3 环路扩频频谱仿真

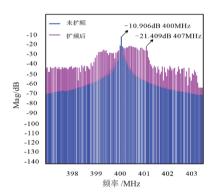

本设计的重点在于扩频对 EMI 的抑制,通过频谱能量对抑制效果的观察和分析,本章对扩频时钟模块电路进行瞬态仿真,再使用离散傅里叶变换对未扩频和扩频后的输出时钟进行计算,再通过 dB20 计算器将其计算 <sup>[8]</sup>,可以得到未扩频和扩频电路的频谱。在满足指标控制电压为 1.8 V,输入时钟频率为 20 MHz,输出时钟频率为 400 MHz 以及扩频深度 -5×10<sup>3</sup> 的情况下进行后仿。

图 10 为未扩频与扩频后时钟模块电路的输出信号频谱图,图中紫色线为扩频后的频谱图,蓝色曲线为未扩频的频谱图。

图 10 扩频与非扩频的输出频谱图

由图 10 可以看到,未扩频的时钟频谱只存在一个峰值在 400 MHz 的位置凸显,而经过扩频后的时钟频谱表现为一个 梯形,扩频后的频谱范围为 399 ~ 401 MHz,扩频深度实现了 -5×10³ 的控制,满足了指标要求。经过对数字控制信号模块的控制,对相位插值器的开关进行偏置,从而对环形压控振荡器的输出进行扩频调制。调制的结果表明,未扩频的电路表明在 400 MHz 的频谱能量为 -10.906 dB,而扩频后的频谱能量在 400 MHz 降低为 -36.42 dB,最高的频谱能量体现在 400.7 MHz 为 -21.409 dB,输出信号的频谱能量较为均匀分布在 399 ~ 401 MHz 中,电磁的干扰降低了 10.32 dB,实现了扩频。表 1 总结了在 PVT 影响在扩频时钟模块电路 [9] 的频谱能量变化。

表 1 在 PVT 影响在扩频时钟模块电路的频谱能量变化

| 工艺角参数          | 频谱能量降低值 /dB |

|----------------|-------------|

| FF -55℃ 1.98 V | 10.11       |

| TT 25℃ 1.8 V   | 10.32       |

| SS 125℃ 1.62 V | 9.67        |

## 4 总结

本文基于 ICS PCIE Gen2 的实际工程运用,在 SMIC 0.18 μm 的工艺下,实现了在传统电荷泵锁相环系统的基础上通过数字控制信号控制相位插值器来完成扩频时钟模块电路的设计,实现了输出频率为 400 MHz,扩频深度为 -0.5%的扩频模式。仿真结果表明,在非扩频情况下的确定性抖动为 31.6 ps,周期间抖动为 5.1 ps,在扩频的情况下输出 400 MHz,扩频 -5×10³的情况下,周期间抖动为 8.6 ps,并且使 EMI 降低了 10.32 dB。

### 参考文献:

- [1]YANG F L, LEE D H, CHEN H Y, et al. 5nm-gate nanowire FinFET[C]//Digest of Technical Papers. 2004 Symposium on VLSI Technology, 2004.Piscataway:IEEE, 2004: 196-197.

- [2] 谭锐. 电磁干扰 (EMI) 抑制技术 [J]. 磁性材料及器件, 2000, 31(1): 28-32.

- [3] CHEN W T, HSU J C, LUNE H W, et al. A spread spectrum clock generator for SATA-II[C]//2005 IEEE International Symposium on Circuits and Systems (ISCAS). Piscataway:IEEE,2005: 2643-2646.

- [4] MOCANU M, GURZUN M, GORAS L. Aspects concerning cycle-to-cycle jitter in a comparator based relaxation oscillator[C]//CAS 2012 IEEE. Piscataway:IEEE, 2012: 425-428.

- [5] 牛晓良. 适用于串行接口的时钟数据恢复电路的设计 [D]. 北京:北京理工大学,2016.

- [6] HEYDARI P. Analysis of the PLL jitter due to power/ground and substrate noise[J]. IEEE transactions on circuits and systems i: regular papers, 2004,51(12): 2404-2416.

- [7] LIU L X, YANG Y T, ZHU Z M. System design of pll based on behavioral model using verilog-A[J]. Chinese journal of electron devices, 2004, 27(2): 324-328.

- [8] 张岩, 张晓明, 王瑜, 等. 基于离散傅里叶变换的频谱分析 新方法 [J]. 电力系统保护与控制, 2011, 39(11):38-43.

- [9] 李方博. 高速串行通信链路扩频时钟发生器关键技术研究 [D]. 上海: 上海交通大学,2019.

#### 【作者简介】

葛浩正(1996—),男,陕西西安人,硕士,助理工程师,研究方向:模拟集成电路。

(收稿日期: 2023-12-14)