# 基于 ADS1115 的 FPGA 接口设计

李雨桐<sup>1</sup> 乔 佳<sup>1</sup> 王 宇<sup>1</sup> LI Yutong QIAO Jia WANG Yu

# 摘 要

随着电子技术的加速发展,更好地处理现实生活中的模拟信号和数字世界中的数字信号,是人们迫切的需求。核心器件 FPGA 实现对 16 位高精度模数转换芯片 ADS1115 的控制。VHDL 硬件描述语言设计  $I^2$ C 总线运行模式。结合 ADS1115 工作时序特点,设计有限状态机,实现对控制电路的逻辑控制。根据 FPGA 结构特点和  $I^2$ C 总线的通信协议,设计相关驱动程序,实现采集单路模拟量。通过对相应电路的实际测量,证明所设计的方案有效、可靠,同时可应用于其它类似的模数转换装置。

关键词

FPGA; ADS1115; I<sup>2</sup>C 总线; 模数转换; 有限状态机

doi: 10.3969/j.issn.1672-9528.2024.03.033

### 0 引言

目前,伴随着通信、计算机和多媒体技术的迅速发展,全世界数字化高新科技领域继续前进,越发需要利用数字系统来处理模拟信号。为满足数字信息时代的加速变迁,用来联系数字世界和现实世界的模数转换技术是重要的突破领域。在电子领域,模数转换器已经出现了多种结构,并且各具特色。本文中对高精度模数转换芯片 ADS1115 进行了全方位的介绍,并探究利用 VHDL 语言控制 ADS1115 的运行,达到模数转换的目的。

### 1 技术概述

ADS1115 是一种超小型、低功耗、内部参考的 16 位数字转换器,通过 I<sup>2</sup>C 总线兼容的串行接口实现数据传输。 I<sup>2</sup>C 总线通过配置 4 个 I<sup>2</sup>C 从地址来操作 4 片 ADS1115; 芯片转换操作的最高采样速率是 860 sps; 其工作电源可以是 2.0~5.5 V; 既可以完成两路差分输入,又可以完成 4 路单端输入,操作模式既可以选择单触发模式,又可以选择连续触发模式;可以辨别的最小模拟量是 256 mV。 ADS1115 外围接口通过配置寄存器来实现两路差分输入和四路单端输入,实现转换模式的选择,并选择适当的采样速率。根据地址指针寄存器中的数据来选择下一步的寄存器,对寄存器进行集成振荡器。根据 ADS1115 的自身特性,当温度和时间发生漂移时,内部振荡器也会受到相应的影读写操作。

$I^2C$  总线支持任何 IC 生产过程(NMOS、CMOS、双极性)。两线包括串行数据总线 SDA 和发送时钟信号总线 SCL。通信的进行是要在两个器件之间完成的。通常将这两

1. 航空工业西安航空计算技术研究所 陕西西安 710065

个器件称为主机和从机。并不是所有的器件既可以作为主机 又可以作为从机,这需要根据芯片设计来确定,在本文中 的 ADS1115 芯片只可以作为从机。I<sup>2</sup>C 总线由两条线组成: SDA 和 SCL。所有数据通过 I<sup>2</sup>C 总线以 8 位传输。传输数据时, I<sup>2</sup>C 总线有其特殊的规定。传输数据时,SDA 线在 SCL 线为 低电平时变成要传输的电平,在 SCL 线为高电平时进行数据 传输。如果 I<sup>2</sup>C 总线上的空闲时间超过 25 ms,则总线超时。

I<sup>2</sup>C 总线以三种速度之一工作。标准模式允许时钟频率 100 kHz; 快速模式 400 kHz; 高速模式 3.4 MHz。ADS1115 与所有三种模式完全兼容,因此不需要采用特别操作,就可以工作在标准或快速模式,但若要使用高速模式,必须采用激活方式。ADS1115 有配置寄存器、转换器寄存器和两个设置比较器阈值的寄存器。通过 I<sup>2</sup>C 接口发送地址指针寄存器来访问各个寄存器,设置相应的比较器模式、操作模式、满量程范围、输入选择和数据速率,确定 ADS1115 的运行状态,并确保整个运行能够顺利完成。

有限状态机的特点和优势如下:一个设计目标可以采用多种多样的逻辑方案来实现。结合自身特点,描述和完成一个设计方案,有限状态机会是最优的选择。通过分析大量设计方案发现,无论是基于 HDL 还是 CPU,FPGA 实现的功能都要比它们优良很多。

本次设计中采用的 FPGA 是暴风四代 EP4CE6E22C8。 以下是 FPGA 所特有的优点。

- (1) 高效的顺序控制模型。FPGA 之所以是实现过程控制高速高效的最佳选择,是因为它优化了传统硬件系统顺序方式上的不灵活。VHDL 语言具有明显的灵活性和方便性,可以控制信号以理想设定的状态运行。

- (2) 方便进行设计上的优化。之所以能够进行设计上

的优化,是因为状态机本身的构建并不是很复杂,语句上的书写又具有一定的特点。对于拥有良好性能的 FPGA,拥有许多可以控制并且自动对状态机进行优化的能力,其中安全状态机的生成和编码方式的选择就是很好的例子。

- (3) 系统稳定性。状态机有助于解决时序电路中出现的竞争冒险现象,提高了系统稳定性。竞争冒险现象的具体概念是在信号通过不同路径的传输同时在一个点处会和,由于路径不同或门电路存在延迟现象,导致信号到达某点的先后顺序有差异,会有错误脉冲输出。

- (4) 高速性能。状态机采用时钟节拍的顺序方式工作。 在工作过程中,CPU 的耗时过长,速度太慢。CPU 的内部运 行是依据指令周期进行的。一项独立操作的运行需要一条指 令周期。一个完整的设计程序既含有运算又含有控制,然而 要实现这些功能,需要的指令是很多的。

- (5) 高可靠性能。特定场所下的电子系统不仅对硬件设施有很高的要求,在设计方案方面要求也是非常严格的。这就需要在设计语言上能有良好的容错性能。对于 CPU 而言,其自身的机构结构特点和软件运行特点决定了它的容错技术不会太高。而状态机的设计特点,允许其快速地从非法状态中跳出,不会影响系统的正常运行。

### 2 硬件电路设计

21 Hbn

SCL

ADS1115 芯片、各引脚及功能如表 1 所示。

| 51脚       | り 形                      |

|-----------|--------------------------|

| ADDR      | I <sup>2</sup> C 总线从地址选择 |

| ALERT/RDY | 数字比较输出或者是转换准备信号          |

| ALERT/RDY | 数字比较输出或者是转换准备信号          |

| GND       | 模拟接地端                    |

| AIN0      | 差分输入1:同相输入端/单通道输入端1      |

| AIN1      | 差分输入1:反向输入端/单通道输入端2      |

| AIN2      | 差分输入 2: 同相输入端 / 单通道输入端 3 |

| AIN3      | 差分输入 2: 反向输入端 / 单通道输入端 4 |

| VDD       | 提供电源: 2.0 ~ 5.5 V        |

| SDA       | 数据输入、输出端口                |

表 1 ADS1115 各引脚及功能

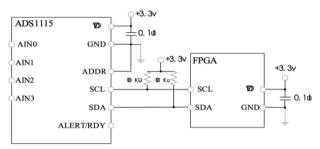

结合芯片的结构特点,利用单极电源 VDD 来提供能量,以确保相应模拟电路和数字电路的正常运行。良好的电源去耦是实现电路最佳性能的重要因素,VDD 必须至少要连接一个 0.1 µf 电容器。当设备处于转换时,0.1 µf 电容器可以提供瞬时脉冲,为电路及时提供所需电流。去耦电容既能够为器件提供能量,又能够作为旁路电容旁路掉高频噪声。一般来说,电容的规格选取并不十分严格,将电容连接在靠近 VDD的地方。

时钟信号输入端

ADS1115 有一个地址引脚 ADDR 配置器件的 I<sup>2</sup>C 地址。GND、VDD、SDA和 SCL 是 ADDR 引脚连接的四个不同状态,以此选择四个不同的地址,分别为: 1001000、1001001、1001010 和 1001011。在本设计中采用单个芯片,不用过多考虑 ADDR 的设计,直接将 ADDR 连接到 GND 即可,确定了ADS1115 的从地址为 Ox48。

由于良好的高速性能,FPGA与高速 ADC 接口十分常见,并行或串行接口都相同。考虑到接口通道的高速性质,为了更好地匹配传输特性阻抗,减少高频信号谐波信号反射波的干扰,应当于每一通道线都穿接一个小电阻,信号的频率越高,阻值就越小。另外,主机和从机之间的连线尽可能短,电阻的物理尺寸尽可能小。因此,硬件连接图如图1所示。

图 1 硬件连接图

### 3 软件设计

### (1) ADS1115 的操作模式

ADS115 有两种操作模式。config 寄存器中 MODE 的设置状态可以设置要采用的操作模式。虽然掉电,但设备仍然响应命令。在config 寄存器中的操作状态位(OS)被写入1时,器件会在短时间内上电,开始进行一次转换。当 MODE 位的状态为0时,ADS1115 进入连续转换模式。一次转换完成后,数据被存放在转换寄存器中(由 FPGA 进行读取),并开始进行下一次转换。在本次设计,采用的是连续转换模式。

上电时,ADS1115 实现复位。此时,config 寄存器中各个位都被自动设置成默认状态。但并不是所有模块都处于不工作状态,其中器件接口和数字模块可以工作,但不会进行数据转换。掉电后,在上电时可能会产生浪涌现象。上电时,I<sup>2</sup>C 总线会发出呼叫复位命令,ADS1115 会进行内部复位操作。

MUX 是 ADS1115 所具有的部分,用来测量四个单端或两路差分信号。多路复用器由配置寄存器中的 MUX[2:0] 位控制。

# (2) 编程设计

在接收模式下,ADS1115 作为从站接收机,在系统中接收数据。FPGA 处于对 ADS1115 写的状态下。ADS1115 无法驱动 SCL 线作为从设备。在从机接收模式下,7位器件地址和 R/W 位组成地址字节进行传输,由主机发送到从机。第二个字节是主机发送的地址指针寄存器,其中 P[1:0] 中的数据

状态决定数据写入的寄存器。主机发送的每个字节都会得到 从机 ADS1115 的应答。

在发送模式下,由7位器件地址和R/W位组成第一个字节进行传输,从主机发送到从机。该字节将ADS1115置于发送模式。转换寄存器中的高低字节先后传输,并得到主机的应答。

此外,利用不确认信号或发送 START 条件和 STOP 条件, 主机可以终止任何字节后的传输。

ADS1115 写入和读取寄存器。发送从机地址,从机的读取状态根据低 R/W 位来选择。

在写状态下,R/W 位为低电平。要访问 ADS1115 的特定寄存器,主机必须首先往从机中的地址寄存器中写入一个适当的值。得到从站确认,主站发出 START 条件,继续向确定的寄存器中写入数据。

在读状态下,主器件发出 R/W 位为高的状态,得到从机应答后,继续发送地址指针寄存器字节,确定要读取的寄存器。

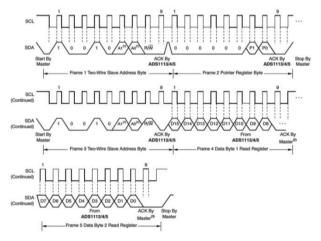

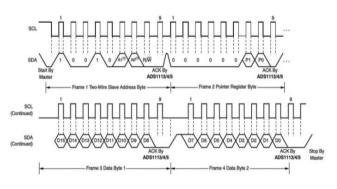

图 2、图 3 分别为读寄存器时序图和写寄存器时序图。 在图中,Start By Master, 主机发送的开始信号。只有在开始条件下,才能进行一系列的操作。ACK, 应答信号, 每次数据传输, 都需要得到应答信号才能继续下一步。Stop By Master, 主机发送的结束条件。

图 2 读寄存器时序图

图 3 写寄存器时序图

### 4 实验设计

### 4.1 总体框图

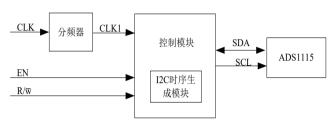

总体设计时包括 1 位时钟线、串行时钟线(SCL)、串行数据线(SDA)、读写控制线。主机控制器应该由分频器模块、控制模块、时序模块组成。最后应用 VHDL 语言,实现模数转换和数据读取的功能。如图 4 所示,CLK 指的是FPGA 板子所带的系统时钟(50 MHz);CLK1 指的是系统时钟经过 500 次分频后的时钟;控制模块是最主要的组成部分,编辑 VHDL 程序完成时序功能;SDA 指的是串行数据双向传输总线;SCL 指的是串行时钟总线。

图 4 总体设计框图

# 4.2 控制模块设计

控制模块需要控制主机产生起始、读写、停止、应答检测、故障分析的状态转换。状态机包括错误状态、开始状态、读写状态、应答状态和结束状态。由于只需要对单路模拟信号进行操作,所以将寻址状态包含在开始状态中,在产生开始条件后,直接发送7位固定地址和读写标志位。

在状态转换过程中出现故障状态即 W=1 时,主机重新返回开始状态,进行数据的传输;在 SDA 开始传输数据时用计数器进行计数,在计数为 8 时,计数器输出 Q=1,设置低电平释放 SDA,等待来自从机的 ACK 应答,进入应答状态。如果 ACK 为无效状态(高电平),则返回开始状态;如果为有效状态(低电平),则进入下一个状态。

FPGA 发送的第一个字节是 ADS1115 地址和确定 ADS1115 处于读或写的一位。将模式设置为连续转换、单端 测量,然后读取转换结果,发送字节。

写入配置寄存器:

第一个字节: ob10010000

第二个字节: ob00000001

第三个字节: ob10000100

第四个字节: ob10000011

写地址指针寄存器:

第一个字节: ob10010000

第二个字节: ob00000000

阅读转换寄存器:

第一个字节: ob100100001

第二个字节: ADS1115 与转换寄存器的 MSB 响应 第三个字节: ADS1115 与转换寄存器的 LSB 响应

#### 5 仿真结果及总结

- (1) 利用分频器,将 FPGA 自带的 50 MHz 进行 500 分 频得到 100 kHz 的传输频率,提供控制模块需要的时钟频率 CLK1。

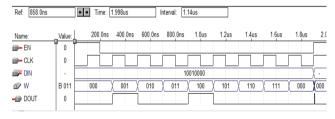

- (2) 在传输模式和接收模式下,每一次数据的传输都是8位,在第9个时钟信号到来之前,SDA总线被主机释放,接收来自从机的应答信号 ACK。如图5所示,EN是数据传输使能信号;CLK是经过FPGA分频后的时钟信号;DIN是主机向从机发送数据的输入端口;W是计数时钟信号,当W为001时,DOUT输出DIN(7),当W为010时,DOUT输出DIN(6)以此类推;DOUT:串行数据输口。

图 5 主机输出串行数据仿真图

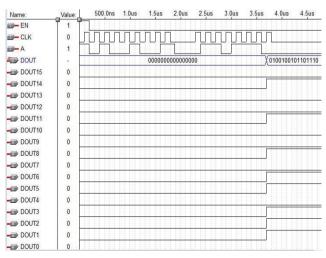

(3)当主机读取从机模数转换后的 16 位数据时,串行数据转换成并行数据,将高低八位数据进行合并,最后存储在 FPGA 的 RAM 中。图 6 中,EN 是数据传输使能信号,由主程序控制产生;CLK 是经过 FPGA 分频后的时钟信号;A 是 SDA 总线的串行数据;DOUT 是 16 位数据的并行输出。

图 6 串行传输转换并行传输仿真图

(4) 在主程序设计中,利用有限状态机,实现对ADS1115 信号的一系列操作。如图 7 所示,EN 是程序使能信号,为高电平时,开始运行程序;CLK 是系统时钟,频率为 50 MHz;WS 是写状态下的从机地址;SUB 是寄存器

地址; RS 是读状态下的从机地址; SDA 是串行数据总线; SCL 是串行时钟总线。

图 7 主程序顶层设计图

本文利用 FPGA 模块与 ADS1115 芯片对单路模拟信号进行采集。分频时,要注意 I<sup>2</sup>C 总线的波特率; 主机传输数据时,要满足 SDA 的输出和 SCL 的时钟是否满足总线协议; 从机发送数据时,要进行串行数据转换并行数据。

# 参考文献:

- [1] 李长才,肖金球,华猛.基于 ADS1115 多通道低功耗环境 参数检测系统设计 [J]. 苏州科技大学学报(工程技术版), 2017, 30(3):77-80.

- [2] 姬占涛, 毛惠丰. TMS320F28335 的  $I^2$ C 总线与 ADS1115 的 通信设计 [J]. 单片机与嵌入式系统应用, 2016,16(1):45-48.

- [3] 宋杰, 陈岚, 冯燕. 一种  ${\rm I}^2{\rm C}$  总线控制器的接口设计 [J]. 信息与电子工程, 2010,8(4):467-470.

- [4] 黄建兵, 段明亮. I<sup>2</sup>C 总线及其在 MCS-51 单片机系统中的应用[J]. 陕西科技大学学报, 2008, 26(1):103-109.

- [5] 张家会, 熊先越, 曾丽珍. 基于 FPGA 的  $I^2C$  总线设计 [J]. 光通信技术, 2011, 35(9): 40-41.

- [6] 潘利明, 王惠平, 刘春风. 基于 FPGA 视频采集中的  $I^2C$  总 线设计与实现 [J]. 现代电子技术. 2010,33(8):80-82.

- [7]沈华,王俞心.基于FPGA的 $I^2$ C总线主控器的设计与实现[J]. 航空计算技术,2007,37(6):109-111.

- [8] 赵辉, 董德存. $I^2$ C. 总线技术及其应用实例 [J]. 微型电脑应用, 2005, 21(4):61-63+66.

- [9] 宋泽明, 陈文楷. 基于 VHDL 的有限状态机设计 [J]. 北京工业大学学报, 2005, 31(1):21-24.

- [10] 石宗义.I<sup>2</sup>C 总线时序分析及其模拟[J]. 太原理工大学学报, 2004, 35(1):53-56.

# 【作者简介】

李雨桐(1996—),女,陕西西安人,硕士,助理工程师,研究方向: FPGA接口设计等。

(收稿日期: 2023-12-26)