# 基于 TUSB2046 的多处理器调试模块设计与实现

吴 超<sup>1</sup> 汪利建<sup>1</sup> 王洋洋<sup>1</sup> WU Chao WANG Lijian WANG Yangyang

## 摘要

针对航空电子设备调试过程中,传统的模块调试方法需要多次在机柜中插拔模块,易造成模块损坏,且调试效率低下的问题,基于 USB\_HUB 控制芯片 TUSB2046IBVF 设计了一款同时适用于不超过 10 模块的实时在线调试电路并实现为调试模块。首先介绍了设计方案的物理架构,其次介绍了模块核心芯片的供电方式、时钟电路、负载的过流保护、与机柜的连接器定义等,最后通过对模块的测试,达到了预定的功能,效果良好。

关键词

通用串行总线集线器(USB HUB);调试模块;多处理器;联合测试行为组织(JTAG)

doi: 10.3969/j.issn.1672-9528.2024.03.026

## 0 引言

在嵌入式系统开发和维护过程中,微控制器(microcontrol unit,MCU)的软硬件调试是嵌入式系统开发和维护的重要环节,高效强大的调试模块及方法可以缩短系统的开发周期和产品的迭代升级周期,增强产品的竞争力。在航空电子领域,综合化模块化的航电处理平台或设备以其特有的优点被广泛应用。一个机箱内置多个功能集成模块的物理架构是此类航电设备的通用物理架构<sup>[1]</sup>,即 VPX 机箱技术。VPX 是基于高速串行总线的新一代总线标准,可提供超大

中国航空工业集团公司西安航空计算技术研究所 陕西西安710068 带宽和超大功率,目前被广泛运用于军事等安全性要求较高以及抗恶劣环境下,国产机载计算机设备多遵循 VPX 总线标准设计制造 <sup>[2]</sup>。VPX 机箱则是基于高速串行总线标准的新一代机箱,其体积坚固,抗干扰能力强且耐震动,内置多个功能模块插槽,普遍应用于服务器、加固计算机等设备,具有高速信号数据采集、实时信号处理及宽频段大容量存储功能 <sup>[3]</sup>。机载计算机无论是在研发阶段以及在装机后,在返修升级过程中都避免不了调试工作的进行。在这一过程中,对产品进行软硬件调试、功能模块程序加载和软件升级等操作时,针对机箱内部的硬件模块目前主流的方法有两种:一种是直接通过模块的起拔器,将各模块从 VPX 机箱内拔出,通过 JTAG 仿真器连接到 PC 机端进行调试工作,完成

- [6]VAN H G, COLE E, BEERY S, et al. Benchmarking representation learning for natural world image collections[C]// Proceedings of the IEEE/CVF conference on computer vision and pattern recognition. Piscataway: IEEE,2021:12884-12893.

- [7]VAN H G, MAC A O, SONG Y, et al. The inaturalist species classification and detection dataset[C]// Proceedings of the IEEE conference on computer vision and pattern recognition. Piscataway: IEEE, 2018:8769-8778.

- [8]DU R, CHANG D, BHUNIA A K, et al. Fine-grained visual classification via progressive multi-granularity training of jigsaw patches[C]// European Conference on Computer Vision. Cham: Springer International Publishing, 2020:153-168.

- [9]YANG X, WANG Y, CHEN K, et al. Fine-grained object clas-

- sification via self-supervised pose alignment[C]// Proceedings of the IEEE/CVF Conference on Computer Vision and Pattern Recognition.Piscataway:IEEE,2022:7399-7408.

- [10] LIANG Y, ZHU L, WANG X, et al. Penalizing the hard example but not too much: a strong baseline for fine-grained visual classification[J/OL].IEEE transactions on neural networks and learning systems,2022.[2023-10-16].https://ieeexplore.ieee.org/abstract/document/9956020

## 【作者简介】

黄文龙(1998—),男,安徽淮北人,硕士,研究方向: 细粒度分类。

马祥星(1998—),女,安徽淮北人,本科,研究方向: 细粒度分类。

(收稿日期: 2023-12-12)

调试后再次插入机箱;另一种是在机柜内预留调试模块,调试模块印制板上集成多个编码开关,每个开关分别控制机柜内不同的功能模块与PC机相连接进行调试,每次调试都需要和方法一那样,将调试模块从机柜拔出并拨动对应的编码开关至"on"。这两种方法都不可避免地需要多次从机箱插拔模块,甚至没调试完毕就再次装入。这样的调试方法给产品本身以及调试工作流程带来了两个严重问题:第一,调试效率低下且模块拔出后需要再次搭建调试环境;第二,在多次反复的插拔过程中易损坏模块和机箱,且易出错,尤其在外场工作时产品的损坏难以迅速替换。因此,设计一款适合多MCU或多模块的实时在线调试模块成为必要[4]。

#### 1 设计原理

#### 1.1 MCU 调试原理

联合测试行为组织(joint test action group, JTAG)调试 技术是目前最有效的嵌入式 MCU 调试方式 [5]。JTAG 是一 种国际标准测试协议,用于集成电路的测试,JTAG协议普 遍应用于多数高级集成电路。目前随着可编程器件技术的快 速发展, JTAG 不单单局限于对电路的测试, 大多数 DSP、 FPGA 芯片都支持由 JTAG 命令配置的方式,而且 JTAG 配 置方式的优先级高于其他任何一种配置方式。基于 JTAG 标 准的调试技术,是在 MCU 芯片内设符合 JTAG 协议标准的 内嵌调试结构和模块,实现对目标 CPU 启停控制。标准的 JTAG 调试接口必须使用 VCC、GND 电源信号, 另外协议接 口采用 4 线, 分别为 TMS、TCK、TDI和 TDO。JTAG 引脚 的定义为: TMS 为测试模式选择,用 TMS 来设置 JTAG 模 块处于特定的测试模式; TCK 为测试时钟的输入; TDI 为测 试数据的输入,测试数据或测试指令通过 TDI 引脚输入; TDO 为测试数据输出,数据通过 TDO 引脚从 JTAG 接口输出。 MCU 一般内嵌 JTAG 接口,程序的下载以及片上存储器的读 写通过 JTAG 接口进行。

# 1.2 USB HUB 原理

通用串行总线集线器(universal serial bus hub,USB\_HUB)是一种用于扩展 USB 接口数量的设备,其内部包含一个至多个集线器控制芯片,可以实现管理和控制数据传输功能 <sup>[6]</sup>,进而将一个 USB 接口扩展至多个,满足产品同时连接多个 USB 设备的需求 <sup>[7]</sup>。USB\_HUB 通常由一个"上游"端口和多个"下游"端口组成,根据 USB 规范,USB\_HUB有两种供电方式,分别为总线供电和单独供电。在总线供电模式下,USB\_HUB 为其每个下游端口提供 100 mA 的电流供负载设备使用;在自供电模式下,可以为每个下游端口提

供最大 500 mA 的电流。原则上,一个 USB 设备可以进行多层级联至 127 个下游端口,但实际使用中由于电流和功率的限制,一般不超过 3 层级联。

## 1.3 过流保护原理

在集成电路中,限流保护电路作为负载芯片的核心,影响整个电路后续的工作状态,因此负载芯片对内部限流保护电路提出了很高的设计要求。当电路中输出负载电流突然超过限流阈值或者出现短路时,负载芯片会流过很大的电流,瞬间电流可能达到10A以上,会极大程度地影响芯片的正常工作。因此,设备将通过主动切换至恒流模式,将输出电流限制到安全水平。一般可以采取限流功率分配开关分别对负载进行限流保护,当连续的过载或者短路情况出现,增加限流开关的功耗,导致设备温度过高时,热保护电路就会主动切断开关防止损坏,内部电路确保开关是保持关闭直到有效的电压输入存在<sup>[8]</sup>。

## 2 电路设计与实现

#### 2.1 方案设计

本章基于 USB\_HUB 控制芯片 TUSB2046IBVF 设计了一个适用于 10 个电子硬件模块或 MCU 的具有供电和 USB 接口调试功能的实时调试系统。

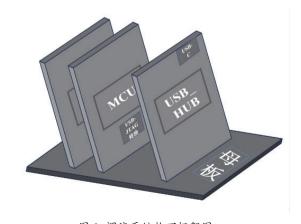

如图 1 所示,调试系统的功能主要由三部分组成,分别为待调试的装有 MCU 的功能模块,具备 USB\_HUB 控制芯片的调试模块,以及连接各功能模块和调试模块的模板,母板上设有电连接器。调试功能主要通过设计的调试模块实现,在机柜内各功能模块所连接的母板上预留调试模块的专用插槽,USB\_HUB 设计在调试模块上。如图 1 所示,各功能模块上的 MCU 通过母板与调试模块相连,进而通过 USB 接口连接至 PC 机,完成调试功能。在调试模块的两端分别设计了 VITA 46 连接器 1410187-3 和 USB-C(USB4085-GF-A),分别与机柜母板和 PC 端相连。

图 1 调试系统物理框架图

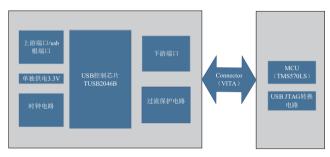

调试模块主体设计上采用 USB\_HUB 架构,本设计具体采用 3 个 TUSB2046IBVF 控制芯片进行三级上下游端口级联,实现 1 转 10 的 USB 接口扩展功能。TUSB2046IBVF有两种供电方式,分别为总线供电、单独供电方式。端口BUSPWR 高电平有效与否,表示下游端口从 USB 总线供电或独立供电。在如上所述的总线供电模式下,USB\_HUB每个下游端口可提供 100 mA 的电流供负载设备使用,而在自供电模式下,每个下游端口最大可以提供 500 mA 的电流。本设计采用三级 TUSB2046IBVF 芯片级联,需要保证每一级的有效电流,故采用各芯片独立供电 3.3 V 的方式保证下游端口的电流损失最小,将 BUSPWR 拉低,此时处于 TUSB2046IBVF 芯片每一级的各下游端口可以提供最大500 mA 的电流。

图 2 调试模块功能框架图

对于时钟输入电路,TUSB2046IBVF 芯片有两种时钟信号输入,分别为6 MHz,50%占空比的晶体信号输入和48 MHz的晶振输入。由于有源晶振稳定性高,抗干扰能力强,且可维修性高,本设计采用48 MHz的晶振时钟信号作为输入,保证了电路的稳定性。由于本设计采用三级芯片进行串联,故本电路采用零延迟时钟缓冲器CY2305SXI-1H,将1路48 MHz的时钟信号输入,转化输出3路同相位的48 MHz时钟信号,分别给3个TUSB2046IBVF提供时钟信号,保持信号的实时性和一致性。此模式下,芯片内部片上振荡器只支持基本频率,具体到TUSB2046IBVF芯片,将TSTMODE和XTAL1管脚3.3 V供电。48 MHz的时钟信号输入至27脚TSTPLL/48MCLK,XTAL2悬空不接。

## 2.2 USB JTAG 转换电路

MCU一般内嵌 JTAG 接口,方便进行程序的下载以及片上存储器的读写等调试工作,但 JTAG 无法直接和 PC 端接口进行物理连接,PC 端一般通过 USB 口进行连接调试。FT2232HL是 FTDI 发布的一款高速 USB 转 UART/FIFO 芯片,具有多种标准协议串行 / 并行接口的配置功能,主要通过多协议同步串行引擎 (multi-protocol synchronous serial engine,MPSSE)提供三种类型的 API 来实现 USB 转 I2C、SPI 和JTAG 等常见接口 [9]。FT2232HL 内有两个独立的 UART/

FIFO 控制器,对应两个独立的转换通道,可分别配置成不同的工作模式。一个 USB 下游端口转换成两个 I/O 通道。每个 I/O 通道可以单独配置成 UART 接口或者 FIFO 接口。通过对外挂 EEPROM 的配置,FT2232HL 还提供一系列新的操作模式,如多协议同步串行机接口,这是专为同步串行协议如 JTAG 和 SPI 总线设计的。

本设计采用 FT2232HL 芯片,通过添加配置电路,实现由单通道电路到双通道串/并口的转换。将 USB 信号转为一路串口通道,便于在调试过程中提供监视功能,另一通道设置为 JTAG 通道,与 MCU 的 JTAG 接口连接共同完成功能模块的调试功能。FT2232HL 上集成了全部 USB 处理协议,使用时不需要另外编写 USB 固件程序。

## 2.3 过流保护电路

本设计共采用3个四限流功率分配开关芯片TPS2044BDRG4分别对负载进行限流保护。每个限流开关控制芯片连接一个USB\_HUB控制芯片TUSB2046IBVF,通过对OC1-OC4输出管脚连接TUSB2046IBVF的OVRCUR1-OVRCUR4,进而通过USB\_HUB芯片的PWRON1-PWRON4管脚控制限流开关芯片的使能开关。TPS2044BDRG4采用5V供电,且常规将OC(x)管脚拉高电平,当输出负载超过限流阈值或出现短路时,设备通过切换到恒流模式,将输出电流限制到安全水平,拉低过流OC(x)逻辑输出。

## 2.4 连接器定义

调试模块和机柜母板的连通采用 VITA 46 连接器连接,调试模块上的子板采用 1410187-3 型号,母板模块上的背板连接器采用 1410140 型号连接器,与 PC 端之间采用 USB-C (USB4085-GF-A) 相连接。本设计中 VITA 46 连接器的定义包括两类: 奇数列含单端信号金手指,偶数列不含差分信号金手指,具体如表 1 和表 2 所示。USB-C 连接器为 16 针中心对称连接器,共有两排管脚,两排各有两路电源信号,两路数据信号分别对应差分数据的正负,还有两路地信号,具体信号如表 3 所示。

表1与背板连接器互连-奇数列定义

| 奇数列晶片(1、3、5、7、9、11、13、15) |                  |                               |  |  |

|---------------------------|------------------|-------------------------------|--|--|

|                           | 子板连接器引脚          | 背板连接器引脚                       |  |  |

| 差分信号                      | $\mathbf{a}_{x}$ | $\mathbf{a}_{x}$              |  |  |

|                           | $b_x$            | $b_x$                         |  |  |

| 差分信号                      | $d_x$            | $\mathbf{e}_{x}$              |  |  |

|                           | $\mathbf{e}_{x}$ | $\mathbf{f}_x$                |  |  |

| 单端信号                      | $g_x$            | i <sub>x</sub>                |  |  |

| 地信号                       | $c_x$ , $f_x$    | $c_x$ , $d_x$ , $g_x$ , $h_x$ |  |  |

表 2 与背板连接器互连--奇数列定义

| 偶数列晶片(2、4、6、8、10、12、14、16) |                       |                                       |  |  |

|----------------------------|-----------------------|---------------------------------------|--|--|

|                            | 子板连接器引脚               | 背板连接器引脚                               |  |  |

| 差分信号                       | $b_x$                 | $\mathbf{c}_{x}$                      |  |  |

|                            | $c_x$                 | $d_x$                                 |  |  |

| 差分信号                       | $\mathbf{e}_{x}$      | $g_x$                                 |  |  |

| 左刀 旧 勺                     | $f_x$                 | $h_x$                                 |  |  |

| 地信号                        | $a_x$ , $d_x$ , $g_x$ | $a_x$ , $a_x$ , $e_x$ , $f_x$ , $i_x$ |  |  |

注: "x"表示晶片列数

表 3 USB接口定义

| 引脚    | 信号   | 引脚    | 信号   |

|-------|------|-------|------|

| A1    | GND  | B12   | GND  |

| A4    | VBUS | В9    | VBUS |

| A5    | CC1  | В8    | SBU2 |

| A6    | Dp1  | В7    | Dn2  |

| A7    | Dn1  | В6    | Dp2  |

| A8    | SBU1 | B5    | CC2  |

| A9    | VBUS | B4    | VBUS |

| A12   | GND  | B1    | GND  |

| SHELL | GND  | SHELL | GND  |

## 3 功能验证

基于 USB\_HUB 设计的调试模块置于调试系统环境中进行功能验证,采用 CCS11.1.0 开发工具进行软件配置 [10]。首先将各功能模块分别和调试模块依次插入 VPX 机箱中,通过母板相连接,调试模块上 USB 一端连接至 PC 机,机上设备管理器会显示出对应的 USB 设备,如图 3 所示。

图 3 USB 设备端口

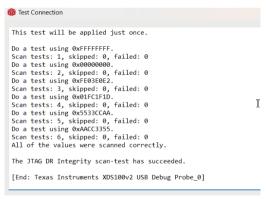

利用 FT2232HL 配置工具配置 MPSSE 通道为一路 JTAG 和一路串口通道,依次对 10 个模块进行调试电路的配置,并应用 MProg 程序按照模块配置不同为 MPROG 设置不同的 USB 序列号,并采用串口调试工具依次显示 10 个不用配置的功能模块序列号。然后任意连接一功能模块,打开CCS11.1.0 进行连接测试,选择项目下"targetConfigs"文件夹的"TMS570LS3137.ccxml"测试文件,点击"Test Connection",结果如图 4 所示,表示连接成功,调试模块达到预期调试功能。

图 4 连接测试结果

## 4 结论

本文基于 USB\_HUB 芯片设计的多模块调试电路,可以用于多项目多环境的调试工作。经过实物的实验验证,所设计的调试模块可以连接 10 个及以下数量的功能模块,并同时提供 USB 接口调试和供电两项功能,在不进行功能模块以及调试模块多次插拔的条件下可以完成机箱内多个模块的在线调试工作和串口监视功能,极大优化了设备软硬件调试过程的流程。

## 参考文献:

- [1] 吕金泽. 综合模块化航空电子软件的测试环境研究 [D]. 北京: 北京化工大学,2017.

- [2] 刘峰. 基于微服务的 VPX 机箱管理系统研究 [J]. 环境技术, 2020, 38(4):7-10+26.

- [3] 尤贵,魏露露,周思远.VPX 机箱的电磁防护设计及测试整改[J].安全与电磁兼容,2020(6):55-59.

- [4] 张克丰. 嵌入式系统的调试方法研究及调试器后台处理模块设计 [D]. 西安: 西安电子科技大学,2023.

- [5] 董哲. 基于 JTAG 的 MCU 调试模块设计与实现 [D]. 西安: 西安科技大学,2013.

- [6] 余和舟, 林飞, 邱志. 基于 USB-HUB 的多串口系统硬件设计 [J]. 现代通信技术,2016(1):32-36.

- [7] 郭敏, 庄信武, 任海波, 等. 基于 USB2.0 的多串口数据采集设计 [J]. 国外电子测量技术, 2017,36(11):75-79.

- [8] 张雪梅, 王玉宏. 基于 TPS2491 的热插拔保护电路设计 [J]. 电子设计工程, 2014, 22(17): 63-66.

- [9] 洪泽,张铆,陈振娇,等.一种基于 SHA-1 身份认证的 FT2232H 程序烧写设备及方法:CN202110400688.2[P]. 2021-04-14.

- [10] 郜丽鹏,王欢,刁鸣. 一种基于 EMIF16 的多核 DSP 上电自启动的简化实现方法:CN201811015884.2[P].2023-11-09.

# 【作者简介】

吴超(1997—),男,陕西西安人,硕士研究生,工程师,研究方向:航空电子系统硬件设计开发。

(收稿日期: 2023-12-22)