# PCB 高速信号仿真技术研究与分析

成伊琼<sup>1</sup> 刘婷婷<sup>1</sup> 秦石明<sup>1</sup> 张文博<sup>1</sup> PANG Yiqiong LIU Tingting QIN Shiming ZHANG Wenbo

# 摘要

文章对 PCB 高速信号仿真技术进行深入研究和分析,介绍高速信号的基本特性及其在 PCB 设计中的挑战,探讨了信号反射、串扰、地弹等现象对信号完整性的影响。为验证 PCB 高速信号完整性仿真工具的性能,设计了几条长度、残桩数量不同的高速信号 PCB 链路,并采用不同的仿真工具对其进行仿真,通过对比不同链路仿真效率以及不同速率下仿真差异,分析总结了不同软件的性能特点,证明了仿真软件在提高产品设计质量和性能方面的有效性。

关键词

高速信号;印刷电路板 (PCB);信号完整性;仿真技术;设计优化

doi: 10.3969/j.issn.1672-9528.2024.12.025

# 0 引言

随着电子技术的飞速发展,高速数字电路已融入生活的方方面面,从智能手机到高性能计算机,都离不开高速电路的支撑,PCB作为电子电路的重要组成部分,其设计质量和性能直接影响到整个电子系统的运行稳定性与性能表现<sup>[1-2]</sup>。特别是对于高密度互连(HDI)技术的应用,PCB的设计和仿真显得尤为重要<sup>[3-4]</sup>。HDI技术对 PCB的布线密度、孔径大小以及焊盘尺寸等方面有着更高要求,这进一步增加了 PCB 设计的复杂度<sup>[5]</sup>。

高速信号在 PCB 中的传输特性与传统信号存在显著差异,主要表现在信号频率高、带宽宽、相位抖动敏感等方面。这些差异性特点对 PCB 的设计提出了新的挑战,传统的设计方法和工具已难以满足需求 <sup>[6]</sup>。因此,开展高速信号在 PCB中的仿真研究对于提升 PCB 设计质量、优化电路性能具有重要意义。

信号仿真技术在 PCB 设计中的应用可以有效预测信号在传输过程中的行为,帮助设计师提前发现并解决潜在问题<sup>[7]</sup>。通过仿真可以模拟信号在 PCB 中的传播路径、反射、串扰等效应,从而评估 PCB 的设计是否符合预期要求。此外,仿真还可以为 PCB 的实际生产提供指导,帮助优化生产流程,提高生产效率<sup>[8]</sup>。

然而,当前高速信号仿真技术仍面临诸多挑战。例如,仿真模型的准确性、仿真算法的效率以及仿真结果的可靠性等都需要进一步研究和解决<sup>[9]</sup>。此外,随着 HDI 技术的不断发展,PCB 的设计越来越复杂,这也给信号仿真技术带来了新的难题。因此,开展高速信号仿真技术的研究,对于推动PCB 设计的进步、提升电子系统的整体性能意义重大。

1. 航空工业西安航空计算技术研究所 陕西西安 710000

本文将对 PCB 高速信号仿真技术进行研究,通过建立 准确的仿真模型、优化仿真算法、提高仿真结果的可靠性等 方法,以期实现对高速信号在 PCB 中传输特性的准确预测和 优化。同时,本文还将探讨如何将高速信号仿真技术应用于 PCB 的设计中,以期为高速电路的设计和制造提供有力支持。

#### 1 PCB 高速电路完整性问题

随着信号工作频率的提升,电路中的模拟特性(如传输线电容、电感效应等)将对电路接收端信号质量产生极大影响,通常将工作频率超过 100 MHz 的信号称为高速信号,也可通过信号上升沿或下降沿陡峭程度确定,由于更陡峭的边沿需要更高频率的信号谐波,快速变化的边沿会导致信号在通过传输线后产生非理性波形,因此也将信号传输延时大于发送端信号波形上升或下降时间一半的电路称为高速电路,高速电路的完整性问题相对于低速电路更为复杂,所以在设计高速信号电路走线时,不仅需要关注信号完整性问题,电源完整性以及电磁辐射于扰问题也不容忽视。

# 1.1 信号完整性问题

信号完整性(signal integrity,SI)问题研究的是信号在 传输过程中的质量问题,表明信号在经过传输线后保持其时 域特性与频域特性的能力,即维持信号功能正确的特性。信 号传输速率提升意味着信号边沿更为陡峭,对应信号有更宽 的有效频谱带宽,而信号高频分量在传输过程中易出现传输 线效应,导致信号质量恶化,常见的传输线效应包括信号的 反射、衰减、串扰等<sup>[10]</sup>,反射是信号在传输过程中阻抗突变 导致的,高速电路常见的阻抗突变结构有过孔、布线几何形 状、封装结构、参考电源/地平面不连续、连接器等,反射 会导致信号的波形产生过冲和下冲以及振铃问题;信号衰减 是由于传输线存在导体损耗、介质损耗、辐射损耗、耦合等 问题,导致信号幅度经过传输线后减小;串扰是指没有电气 连接的传输线之间耦合产生感应电流与感应电压的现象,将 引起信号线上的噪声,由于 PCB 板集成度的提升,板内布线 密度越来越大,也进一步加重了串扰现象。

# 1.2 电源完整性问题

电源作为整个电子产品的"心脏",其设计直接关系 到产品设计的成功与否, 进而引入了电源完整性 (power integrity, PI) 问题, 电源完整性研究的目标是为系统提供稳 定的电压与充足的电流,同时避免噪声在电源分配网络(power delivery network, PDN) 内的进一步传播, PDN 是一个从电 源模块开始经过电路、封装、芯片, 最后到晶体管的分层电 源网络,要求具有低目标阻抗以及高噪声隔离特性。PI 仿真 关注的问题包括直流压降、电流密度、电-热关系、源/地 反弹与同步开关噪声(SSN)等,芯片管脚电平切换产生的 瞬态电流(ΔI噪声电流),由于源/地反弹问题将在电源平 面或地平面产生 ΔI 噪声电压或 SSN 噪声,这些噪声对于电 路系统的 SI 和 PI 都将产生严重影响。

## 1.3 电磁辐射干扰问题

在高速电路中,一些短的布线如芯片引脚、各类插接件、 传输线等都有可能形成发射天线, 向空间辐射能量, 对电路 造成干扰,即 EMI 辐射。在设计高速电路时针对 EMI 问题 应关注干扰噪声源、干扰传输途径以及被干扰对象, 通过干 扰传输途径的不同可将 EMI 干扰分为传导干扰和辐射干扰, 通过产生干扰电流性质的不同可将 EMI 辐射可分为差模辐射 和共模辐射,差模辐射远场的强度随信号频率增大线性增加, 而差模辐射远场的强度与频率平方成正比,高频下的 EMI 问 题会更严重。因此,随着电路频率的提升, EMI 问题已经成 为 PCB 电路设计过程中不可忽视的部分。

# 2 高速电路完整性问题协同分析

高速电路完整性问题都基于相同的电磁原理, 三者相互 作用、相互影响,如电源/地平面上的噪声(PI)会产生的 共模辐射(EMI); 高速信号跳变边沿的高频分量易导致高 频 EMI 辐射。因此,在进行 PCB 电路设计时,对于 SI、PI 以及 EMI 问题应综合考虑、协同分析,这对设计人员提出了 更高要求。

# 2.1 SI/PI/EMI 仿真分析

随着芯片传输速率的提升,高速电路 PCB 设计所面临的 SI/PI/EMI 问题变得更为复杂,且难以直接评估,传统 PCB 电路设计方法是将 PCB 板直接加工制作出来后通过测试确定 电路性能是否能满足系统预期功能要求, 如无法满足, 就需 从设计图开始修改, 并再次进行加工测试, 如此反复, 直至 产品合格,该方法会导致产品生产研发成本的提升,造成大 量浪费。近年来随着各类 EDA 仿真软件的出现,新的 PCB 电路设计方法可以在设计阶段就对产品的 SI/PI/EMI 性能进 行分析优化,极大缩短了产品的研发周期,节约了人力物力,

本文针对应用最为广泛的几类 EDA 软件进行仿真分析,研 究不同软件仿真性能,为后续针对不同电路制定仿真方案提 供依据。下面对电路性能评估指标——"S参数",以及仿 真软件进行简要介绍。

#### 2.2 S参数

S参数针对完整性问题又被称为行为模型,可用于描述 无源线性互连的行为, PCB上的互连包括电阻器、电容器、 电路板走线、电路板平面、连接器、封装等元器件。当信号 激励通过互连后会产生一个响应信号,激励-响应波形中隐 含着该互连的行为模型,即S参数。S参数中隐含了互连的 大量信息,通过这些信息可获知互连的一些特性,如阻抗曲 线、串扰大小、差分信号衰减程度等,基于此,可以通过S参数预估任意信号与互连的作用方式, 推算出任意信号通过 该互连后的输出波形。

S参数描述了互连对入射信号产生的影响,S参数中的"S" 表示散射(Scattering)的意思,信号进入与离开互连的始末 端称为端口,通常将散射回源端的信号波称为反射波,通过 互连散射出去的信号波称为传输波,S参数即表示为从被测 互连的某个特定端口散射出的正弦波与入射到该被测互连某 个端口信号正弦波的比值,即:

$$S = \frac{\text{$\hat{m}$ \text{\frac{\psi}{m}$ \text{$\psi$ twitter}}$}}{\text{$\hat{m}$ \text{$\psi$ twitter}$}} \tag{1}$$

式中: S 参数的值包括幅值和相位两个数值,目前常用 dB 值 描述 S 参数的幅值,dB 通常表示能量的比值,故 dB 值与幅 值之间进行转换时需使用系数 20, 即:

$$S_{\rm dB} = 20 \times \log \left( S_{\rm mag} \right) \tag{2}$$

式中:  $S_{max}$  表示 S 参数幅值的数值。

对于多端口互连,为区分不同S参数涉及的端口,使用 两个下标值,即 $S_{ii}$ ,第一个下标值对应输出端口,第二个下 标值对应输入端口,每个S参数可表示为:

$$S_{kj} = rac{ 输出端口 k 的正弦波}{ 输入端口 j 的正弦波}$$

(3)

式中:对于有n个端口的互连,其S参数可表示为S参数矩阵,

$$\mathbf{S} = \begin{array}{cccc} S_{11} & S_{12} & \cdots & S_{1n} \\ S_{21} & S_{22} & & S_{1n} \\ \vdots & & \ddots & \vdots \\ S_{n1} & S_{n2} & \cdots & S_{nn} \end{array} \tag{4}$$

式中:S参数矩阵元素包含互连的解析信息,实际上代表了 互连的行为模型,可通过仿真工具解析互连行为的有效信息, 从而评估目前互连的状态是否符合实际需求。对于所有线性 无源元件,总有 $S_{k}=S_{k}$ ,故n端口互连的S参数矩阵中独立 元素的个数为:

$$N = \frac{n(n+1)}{2} \tag{5}$$

式中:对于一个 2端口互连的 S 参数矩阵内包含三个独立元素: $S_{11}$ 、 $S_{22}$  和  $S_{21}$ 。其中  $S_{11}$  又被称为反射系数, $S_{21}$  项又被称为传输系数,在实际仿真应用过程中,常用 dB 值来表示这两个系数,故  $S_{11}$  dB 值的绝对值称为返回损耗, $S_{21}$  dB 值的绝对值称为通入损耗被广泛用于描述互连状态的测量术语。

#### 2.3 仿真软件

ANSYS 电子自动化设计(EDA)软件来自著名的 Ansoft 公司,是业界仅有的一套完整的系统电路与电磁场全集成化设计平台,能够完成从部件设计、电路仿真优化到系统仿真验证的全流程,其工具可用于 EDA 软件的电路完整性分析,HFSS(high frequency structure simulator)与 SIwave,均可完成对 PCB 内信号线路的仿真分析,已被广泛应用于 SI/PI/EMI 仿真分析中。

HFSS 基于频域有限元技术的三维全波电磁场求解器,可实现提取 S 参数、显示三维电磁场图、生成远场辐射方向图、提供全波 SPICE 模型的功能,使用 HFSS 工具可以评估PCB 上连接器、高速串行信号走线、过孔以及高速元件等产生的完整性问题。HFSS 将三维建模、电磁场仿真与结果后处理集成于一体,可对设计中任意三维结构实现从直流到几十 GHz 范围内的全波仿真,并以 S 参数进行显示,对于分析高速信号走线的传输特性、反射特性以及匹配特性十分简便。

SIwave 可导入 PCB 和封装等复杂结构的互连模型,通过电磁场仿真技术提取信号和电源的分布参数,获取信号插入损耗、返回损耗、远端串扰(FEXT)、近端串扰(NEXT)、差分 S 参数等。SIwave 采用全波有限元算法分析高速 PCB 单板和复杂 IC 封装上的谐振、反射、串扰、同步开关噪声、电源 / 地弹等特性,适用于精确快速分析包含大规模复杂电源、地平面的 PCB 和封装设计,SIwave 采用混合场求解技术,适合对多层平面结构 PCB 和封装结构提供直流、频域、时域分析。

## 3 仿真方案及结果分析

## 3.1 仿真方案设计

为验证电路完整性分析软件 "HFSS"和 "SIwave"的仿真性能,本文从长度、Stub (残桩)数量两个维度设计了3条不同链路结构的 PCB 电路,链路结构参数如表 1 所示,分别通过 "HFSS"和 "SIwave"对 3 条链路的高速传输性能进行无源仿真,仿真频率范围设置为 0 GHz 到 28 GHz,仿真结果以 S 参数给出,即"返回损耗"与"插入损耗"。

表1仿真链路参数 上腔 /mil

|      | 长度 /mil | 残桩数量 |

|------|---------|------|

| 链路1  | 1 256.3 | 2    |

| 链路 2 | 603.4   | 2    |

| 链路3  | 1 301.2 | 6    |

# 3.2 仿真结果分析

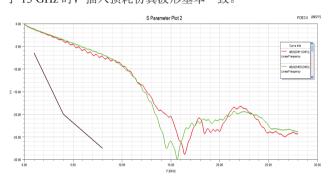

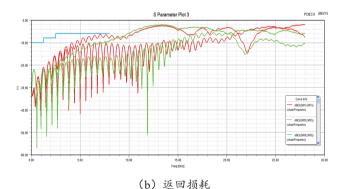

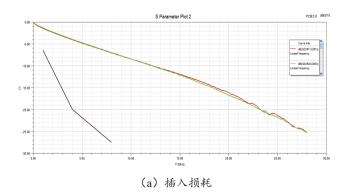

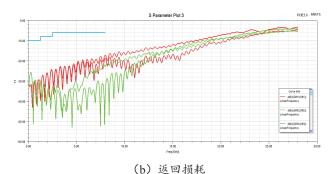

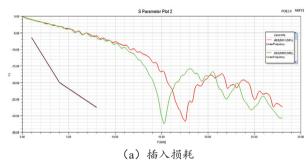

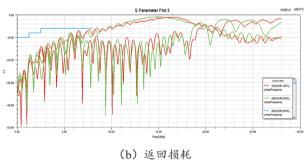

链路 1/2/3 的仿真结果如图 1~图 3 所示,图中曲线分别表示 HFSS 和 SIwave 的仿真结果,可以发现,对于图 1 中链路 1,当仿真频率小于 12 GHz 时,HFSS 和 SIwave 插入损耗的仿真结果基本一致,当仿真频率范围对于 12 GHz 时,仿真结果开始出现较大偏差,当仿真频率小于 15 GHz 时,返回损耗的仿真结果波形略有偏差,但基本变化趋势一致,当仿真频率大于 15 GHz 时,仿真结果开始出现明显的不一致;对于图 2 中链路 2,在整个仿真频率范围内,插入损耗的仿真结果之形偏差较大,当仿真频率小于 13 GHz 时,仿真结果波形偏差较大,当仿真频率大于 13 GHz 时,仿真结果波形偏差较大,当仿真频率大于 13 GHz 时,仿真被形变化趋势基本一致;对于图 3 中链路 3,在整个仿真频率范围内,返回损耗的仿真结果基本一致,但插入损耗在仿真频率大于 10 GHz 时的仿真结果波形偏差较大,在小于 13 GHz 时,插入损耗仿真波形基本一致。

(a) 插入损耗

图 1 链路 1 仿真性能图

图 3 链路 3 仿真性能图

从仿真结果可以看出,对于不同链路, HFSS 和 SIwave 的仿真结果在不同频段有所差异。另外,如表 2 所示,通过 HFSS 和 SIwave 仿真所需时长也不同,这主要是由于这两类 软件所采用算法不同,HFSS 是 3D 全波电磁场仿真工具,基 于有限元理论,理论上计算结果的准确度不受频率影响,因 此对于高频段也可做到精确仿真, 但所需占用的计算资源也 更多,对于计算机的性能有更高要求,SIwave 是 2.5D 的电 磁场仿真工具,其算法假设 PCB 垂直方向上的电磁场是均 匀分布的,因此更适合对低频段的信号进行仿真。HFSS 和 SIwave 都可生成频域 S 参数模型,能够直观显示互连系统在 仿真频段内的传输特性, 但两者仿真精度与仿真时长有所差 异,结合3条链路的仿真结果分析,当信号传输频率小于10 GHz时,采用 SIwave 仿真可在保证精度的同时节约仿真时间。

表 2 各链路仿真时长

单位· h

|      |                 | 1 1           |

|------|-----------------|---------------|

| 链路   | $T_{ m SIwave}$ | $T_{ m HFSS}$ |

| 链路1  | 1.6             | 5.6           |

| 链路 2 | 0.9             | 3.1           |

| 链路 3 | 1.7             | 5.8           |

# 4 结论

本文分析了信号完整性、电源完整性以及电磁辐射问 题对于 PCB 高速电路产生的影响,对当前主流 EDA 软件 ANSYS 的 PCB 完整性分析软件 HFSS 和 SIwave 进行了介绍, 设计了3条高速链路仿真对比这两种软件的仿真精度,对两 种软件的仿真性能进行了分析,基于仿真结果为 PCB 高速电 路完整性问题的仿真工作提供了建议,通过高效仿真使得工 程师在 PCB 设计阶段就可掌握产品的工作性能,有效缩短了 产品研发周期,并进一步降低了研发成本。

#### 参考文献:

- [1] 高晓宇. 信号完整性: 深入理解高速数字电路设计 [M]. 北 京:清华大学出版社,2020.

- [2] 陈世强, 刘明, 姚三坤, 等. 高速 PCB 传输线信号完整性 设计要点研究[J]. 云南民族大学学报(自然科学版), 2024, 33(3): 368-376.

- [3]ANIL K P, AMIT J, SUJANTH N. Signal integrity and compliance test of DSI and CSI2 serial interface over MIPI D-PHY[C]// 2020 IEEE 24th Workshop on Signal and Power Integrity(SPI). Piscataway: IEEE, 2020:1-4.

- [4] WANG L X, ZHANG Y X, ZHANG G. Power integrity analysis for high-speed PCB[C]//2010 First International Conference on Pervasive Computing, Signal Processing and Applications. Piscataway: IEEE, 2010, 106(10): 414-415.

- [5] 邓宇阳. 高速数字信号传输链路建模仿真研究 [D]. 广州: 华南理工大学,2023.

- [6] 贡维,李岩,许泗强,等.电源开关噪声耦合干扰高速信 号的分析及优化方法研究[J]. 计算机工程与科学, 2023, 45(10): 1763-1769.

- [7] 聂俊英. 利用 SigXplorer 进行高速信号仿真研究 [J]. 科技 与创新, 2023(17): 92-94+97.

- [8] 杨云普, 王青, 曾燕萍. 串行链路 IBIS-AMI 模型信号完整 性分析及优化 [J]. 无线电工程,2024,54(4):882-891.

- [9] 李少聪, 杨录, 吕俊文, 等. Flip Chip 结构的 IC 信号完整 性仿真分析 [J]. 单片机与嵌入式系统应用,2023,23(10):12-

- [10] 孙婷, 王冲. 高速数字电路信号完整性分析 [J]. 电子测试, 2021(12):57-58.

# 【作者简介】

庞伊琼(1998-),女,陕西宝鸡人,硕士研究生,研 究方向: 高速信号仿真。

(收稿日期: 2024-08-26)