# 时间敏感网络的时间同步设计与 FPGA 实现

李耀成 常可铮 杨得武 LI Yaocheng CHANG Kezheng YANG Dewu

#### 摘 要

在现代网络系统中,时间同步是实现高效、精确数据传输和协调操作的关键技术,尤其在时间敏感网络 (TSN) 中尤为重要。时间敏感网络旨在提供低延迟、高可靠性和确定性的网络服务, 这对时间同步提 出了严格要求。因此,文章主要探讨了时间敏感网络中的时间同步设计及其在 FPGA (现场可编程门阵 列)上的实现。首先,介绍了传统以太网的局限以及时间敏感网络的概念,根据时间敏感网络中的时间 同步需求,特别是精确时钟同步对系统性能的影响,设计了一种基于 IEEE 802.1AS 的时间同步方案。 该方案通过链路延迟修正与时间同步算法,提升了同步精度。其次,详细描述了该同步方案在 FPGA 上 的实现过程。FPGA 作为硬件平台,能够提供高效的处理能力和灵活的定制功能。并介绍了 FPGA 在实现 中的关键技术,包括以太网协议栈的实现、精确时间戳的生成与管理、链路延迟的测量、频率偏差的修 正以及时钟同步模块的设计。通过 FPGA 的并行处理特性, 实现了对时间同步协议的快速响应和高效执行。 最后,通过实验和测试验证了该同步方案在 FPGA 上的实现效果。结果表明,基于 FPGA 的时间同步方 案能够将时间同步的精度稳定在 300 ns 以内,满足实际应用中时间敏感网络的要求,这一研究不仅为时 间敏感网络中的时间同步提供了有效的解决方案,还为未来相关领域的进一步研究和应用奠定了基础。

# 关键词

时间敏感网络; IEEE802.1AS; 时间同步; 链路延迟测量; FPGA

doi: 10.3969/j.issn.1672-9528.2024.12.020

### 0 引言

传统以太网技术自1973年提出以来,凭借其较高的传 输带宽、广泛的开放性和良好的可扩展性,迅速在IT 领域取 得了显著地位,成为最广泛应用的通信协议标准,并推动了 生产和生活方式的革新。然而,随着时代的发展,在现代网 络系统中,随着对实时性和可靠性的要求不断提高。传统互 联网主要提供尽力而为服务, 虽然在普通应用场景下表现良 好,但在时间敏感网络中往往无法满足严格的同步要求。

进入21世纪后,随着标准以太网的普及和成本降低,基 于以太网的实时总线技术,如 Ethernet/IP[1] 和 EtherCAT[2], 得到了迅速发展。然而,实时以太网技术通常不支持交换机 网络, 其轮询机制 (例如 Ethernet/IP) 或集束帧技术 (例如 EtherCAT)使得标准以太网与实时以太网在同一网络中无法 兼容。

由 IEEE802.1 任务组提出的时间敏感网络(time sensitive network, TSN) 协议簇则弥补了传统以太网的不足之处。时 间敏感网络作为一种关键技术,已经广泛应用于工业自动化、 汽车电子、金融交易等多个领域。TSN 的核心优势在于其能

1. 西北机电工程研究所 陕西咸阳 712000

够提供低延迟、高精度和确定性的通信服务,而这一切的基 础是精确的时间同步。时间同步不仅影响到数据传输的稳定 性,还直接关系到系统的整体性能和安全性。

TSN 在 IEEE802.1AS 同步协议提供的高精度时钟同步基 础上,通过门控时隙调度、路径冗余和帧抢占等优化手段, 显著提高了以太网在实时应用中的表现[3]。

IEEE802.1AS 同步协议作为应对高精度同步需求的重要 标准,其引入了更高精度的时间戳和校正机制,显著提升 了同步精度。通用精准时间同步协议(generalized precision time protocol, gPTP) 提供了 µs 级的精度,确保了时间敏感 网络的稳定运行。然而, gPTP 的实现对硬件的处理能力提出 了更高的要求,特别是在大规模、高速网络环境中,传统的 软件实现往往难以满足实时性的要求。

FPGA (现场可编程门阵列) 凭借其高度的并行处理能 力和灵活的硬件配置,成为实现高精度时间同步的理想平台。 通过在 FPGA 上实现 gPTP 协议,可以将时间同步过程中的 关键操作加速,从而在保持高精度的同时降低延迟。

#### 1 TSN 协议簇

IEEE802.1AS 协议是 TSN 中的一个子协议,专门用于 实现时间同步功能, 也被称为通用精准时间同步协议。该协 议基于 IEEE1588 协议发展而来,通过统一多种时钟类型,使其适用于高精度时间同步场景。IEEE802.1AS 协议定义了以太网网络中的时间同步标准,主要用于在局域网内实现所有时间感知节点的高精度时间同步<sup>[4]</sup>。gPTP 域模型是IEEE802.1AS 协议的核心概念之一,它描述了一系列符合协议要求的时间感知系统和通信链路,这些系统通过同步参考时钟实现精确的时间同步<sup>[5]</sup>。

在 IEEE802.1AS 协议中,报文分为事件报文和普通报文 两类。事件报文在传输过程中会生成时间戳,而普通报文则 不需要。普通报文包括跟随报文、信号报文、对等延迟响应 报文和通知报文。

在 IEEE802.1AS 协议中,共定义了七种报文类型 <sup>[6]</sup>:

Sync、Follow\_Up、Pdelay\_Req、Pdelay\_Resp、Pdelay\_Resp

Follow\_Up、Signaling 和 Announce。 其 中,Sync、Pdelay\_

Req 和 Pdelay\_Resp 属于事件报文类别; Follow\_Up、Pdelay\_

Resp\_Follow\_Up、Signaling 和 Announce 则是普通报文。具

体来说,Follow\_Up 是跟随报文; Pdelay\_Resp\_Follow\_Up 是

对等延迟响应跟随报文; Signaling 是信号报文; Announce 是

广播报文。

在 IEEE802.1AS 协 议 中,Pdelay\_Req、Pdelay\_Resp 和 Pdelay\_Resp\_Follow\_Up 报文用于测量相邻时钟间的链路延迟。Announce 报文携带最佳主时钟的信息,帮助构建整个gPTP 域的主从时间同步拓扑; Sync 和 Follow\_Up 报文负责传递主从节点之间的时间同步信息; Signaling 报文则用于配置报文的发送时间间隔。

# 2 时间同步原理

### 2.1 链路延迟测量

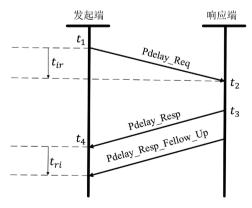

IEEE802.1AS 采用点对点(peer to peer,P2P)的延迟机制来计算链路中每个端口之间的链路延迟  $^{[7]}$ 。链路延迟测量原理如图 1 所示。

图 1 链路延迟测量原理图

在链路延迟测量阶段,发起端和响应端之间使用 Pdelay\_ Req、Pdelay\_Resp 和 Pdelay\_Resp\_Follow\_Up 报文传输延迟 信息。具体链路延迟测量流程如下:

- (1)  $t_1$  时刻发起端向响应端发送 Pdelay\_Req 报文,并记录报文发送时刻的时间戳  $t_1$ 。

- (2) 响应端接收到 Pdelay\_Req 报文时,记录报文到达时刻的时间戳为  $t_2$ 。

- (3)  $t_3$  时刻响应端向发起端发送 Pdelay\_Resp 报文,报文中携带时间戳  $t_3$  信息,并记录报文发送时刻  $t_3$ 。

- (4)响应端在完成向发起端发送 Pdelay\_Resp 报文之后,响应端向发起端发送携带时间戳  $t_3$  信息的 Pdelay\_Resp\_Follow\_Up 报文。发起端接收到响应端发送的 Pdelay\_Resp报文时,记录报文到达的时刻的时间戳  $t_4$ ,并解析出报文所携带的时间戳  $t_5$ 。

- (5) 发起端接收到响应端发送的 Pdelay\_Resp\_Follow\_ Up 报文后,解析出报文所携带的时间戳 *t*<sub>3</sub>。

通过上述链路延迟测量过程,发送端获取了 4 个时间戳:  $t_1$ 、  $t_2$ 、  $t_3$  和  $t_4$ 。根据两个方向的时间差值计算传播延时,相邻节点之间的链路延迟 Delay 公式为:

$$t_{ir} = t_2 - t_1 \tag{1}$$

$$t_{ri} = t_4 - t_3 \tag{2}$$

Delay =

$$\frac{t_{ir} + t_{ri}}{2} = \frac{(t_4 - t_1) - (t_3 - t_2)}{2}$$

(3)

### 2.2 频率偏差修正

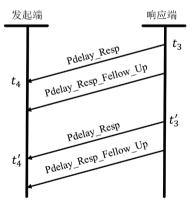

在实际应用中,因为晶振频率偏差的因素,各网络节点的时钟频率并不是完全相同,因此需要对各网络节点间频率偏差进行测量,从而减小时间同步过程中各网络节点间频率偏差带来的影响。频率偏差测量原理如图 2 所示。

图 2 频率偏差测量原理图

频率偏差测量流程跟链路延迟测量的流程基本相同,在链路延迟测量的 Pdelay\_Resp 与 Pdelay\_Resp\_Follow\_Up 报文之后,再发送一组 Pdelay\_Resp 与 Pdelay\_Resp\_Follow\_Up 报文,记录下  $t_3$ 、 $t_4$ 、 $t_3$ '和  $t_4$ '时间戳信息。可以得到响应端和发起端之间的频率比  $t_8$ !8。

频率比值计算结果为:

$$r = (t_3' - t_3)/(t_4' - t_4) \tag{4}$$

引入频率比值的传播延时为:

Delay =

$$\frac{r \times (t_4 - t_1) - (t_3 - t_2)}{2}$$

(5)

#### 2.3 时间同步原理

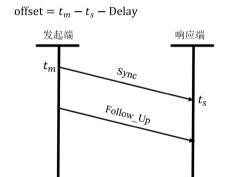

在 IEEE802.1AS 协议中,主时钟节点负责将时间同步信息传递给所有直接连接的时间感知节点。各节点根据传播延迟调整接收到的时间,并在担任中继节点时,将调整后的时间信息进一步传递给其他节点,从而实现整个 gPTP 域内节点的时间同步 <sup>[9]</sup>。同步消息会周期性地从主节点发送到从节点,以便计算它们之间的时间偏差。

时间同步原理如图 3 所示。发送端将 Sync 事件报文发送到响应端端口。发送端在成功发送后生成时间戳  $t_m$ ,响应端在收到 Sync 报文后记录时间戳  $t_s$ 。随后,发送端发送包含时间戳  $t_m$  的 Follow\_Up 报文,响应端在收到该报文后提取时间戳  $t_m$ 。通过之前测量的发送端到响应端的路径延迟 Delay,可以计算出 B 节点与 A 节点之间的时间差 100:

图 3 时间同步原理图

#### 3 系统设计与测试

本文选用 Xilinx 公司的 Artix-7 系列 FPGA XC7A100T-FGG484 来进行本次时间同步系统的设计。该 FPGA 具有 100K Logic Cells,满足本次时间同步系统设计的要求。

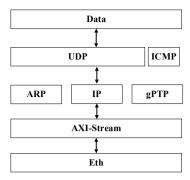

#### 3.1 以太网协议栈

在时间敏感网络的设计中,首先需要在 FPGA 中实现以太网 MAC 层协议栈,其中包括 ARP 协议、IP 协议、ICMP 协议、gPTP 协议以及 UDP 协议,如图 4 所示。FPGA 通过 RGMII 总线与以太网 PHY 芯片相连接,在接收以太网数据时,首先 FPGA 将端口接收到的 RGMII 数据转换 AXI-Stream 总线格式进行传输。使用流水线的方式分别将 Eth 帧头、IP 头部、UDP 头部、UDP 数据以及 ARP 报文、ICMP 报文和 gPTP 把报文分离出来,并缓存到片上 RAM 中。发送以太网数据的过程与接收过程相似,FPGA 将待发送的以太网数据完成相对应协议的组帧,最后以 RGMII 总线发送给以太网 PHY 芯片。

图 4 以太网协议栈原理图

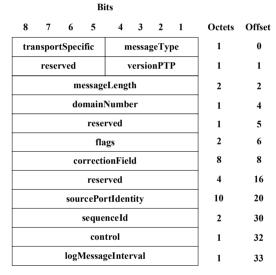

# 3.2 gPTP 报文

(6)

使用 IEEE802.1AS 协议进行时间同步时,gPTP 事件报 文中记录了报文发送与接收过程中产生的时间戳,这些时间 戳中记录了报文发送与接收的准确时刻,如图 5 为 gPTP 报 文格式。

图 5 gPTP 报文格式示意图

在FPGA中将gPTP格式的报文添加到以太网协议栈中,设计了链路延迟、频率测量的Pdelay引擎和时间同步的Sync引擎,在报文的收发过程中计算得出所需的时间戳信息。

#### 3.3 测试与验证

为了验证设计本设计时间同步效果,搭建了一个板级测试系统,能够进行点对点测试。选用正点原子达芬奇 Pro 开发板作为硬件测试平台,该开发板采用 Artix-7 系列 FPGA,型号为 XC7A100T-FGG484,开发板具有千兆以太网接口,使用 YT8511 作为以太网 PHY 芯片。

如图 6 所示,具体使用一根网线连接两块 FPGA 开发板的网口,并使用示波器的两个通道分别接入两块 FPGA 开发板的 IO 引脚。两块 FPGA 中部署本次设计的时间同步算法,通过网线相连进行时间同步后,通过示波器观察两个开发板 IO 引脚上的脉冲信号来检测时间同步性能。

图 6 板级测试连接图

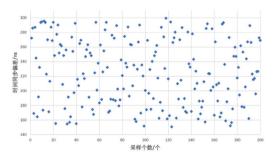

通过板级测试平台,首先发送 Pdelay\_Req 报文进行链路延迟测量与频率偏差测量,之后每 2 s 发送一次 SYNC 报文同步进行时钟同步,如图 7 所示。

图 7 时间同步偏差测量数据

最终测试结果表明,两块 FPGA 开发板间的时间同步精度为,满足 IEEE802.1AS 的精度标准要求。

经多次测试后,选取 200 组样本数据,时间偏差主要分布在 150~300 ns 范围之内,最大偏差值为 289 ns,平均偏差为 220 ns。通过板级测试,验证了本系统时间同步功能的正确性,证明了该系统能够满足 300 ns 的时间同步精度要求,能够满足工业、军工行业的时间同步要求。

# 4 结语

本文设计了时间敏感网络的时间同步方法,并且将该算法部署到FPGA中进行了实现。分析了IEEE802.1AS协议的远了,设计了链路延迟测量算法、频率偏差修正算法与时间同步方法,在FPGA实现了以太网协议栈与精准时间同步协议gPTP,将所设计的链路延迟测量算法、频率偏差修正算法与时间同步方法与以太网协议栈相融合。最后设计了板级时间同步实验,验证了该系统的时间同步精度能够在稳定在300 ns 以内,达到了预期目标。

# 参考文献:

- [1] Emerging Technologies and Factory Automation[C]. Piscataway: IEEE, 2024.

- [2] JANSEN D, BUETTNER H. Real-time ethernet the etherCAT solution[J]. Computing & control engineering journal, 2004,15(1):16-21.

- [3] DITZEL G A, DIDIER P. Time sensitive network (TSN) protocols and use in EtherNet/IP systems[C]//2015 ODVA

- Industry Conference & 17th Annual Meeting. Texas: IEEE Press, 2015:1-24.

- [4] MESSENGER J L.Time-sensitive networking: an introduction[J].IEEE communications standards magazine, 2018, 2(2): 29-33.

- [5] STRIFFLER T, SCHOTTEN H D.The 5G transparent clock: synchronization errors in integrated 5G-TSN industrial networks[C/OL]//2021 IEEE 19th International Conference on Industrial Informatics(INDIN). Piscataway: IEEE,2021[2024-06-18]. https://ieeexplore.ieee.org/document/9557468.

- [6] KIM L S, PARK C, PARK S K, et al. Design of single stream reservation class for efficient data transmission in IEEE 802.1 AVB networks[C]//2015 IEEE 12th Malaysia International Conference on Communications (MICC). Piscataway: IEEE, 2016:135-138.

- [7] DIARRA A, HOGENMUELLER T, ZIMMERMANN A, et al. Improved clock synchronization start-up time for switched ethernet-based in-vehicle networks[C]//2015 IEEE 20th Conference on Emerging Technologies & Factory Automation (ETFA). Piscataway: IEEE, 2015:1-8.

- [8] VAL I, SEIJO Q, TORREGO R, et al. IEEE 802.1AS clock synchronization performance evaluation of an integrated wired—wireless TSN architecture[J].IEEE transactions on industrial informatics, 2022, 18(5): 2986-2999.

- [9] CHUNG H Y, KIM J H, JEON J W. Performance analysis of ethernet power link applied to ethernet of in-vehicle network[C]//Proceedings of the FISITA 2012 World Automotive Congress, v. 6. Vehicle Electronics. Berlin: Springer, 2013:705-714.

- [10] LIM H K, HERRSCHER D, VOLKER L, et al. IEEE 802.1 AS time synchronization in a switched Ethernet based incar network[C/OL]//2011 IEEE Vehicular Networking Conference (VNC). Piscataway: IEEE, 2011[2024-06-22]. https://ieeexplore.ieee.org/document/6117136.

# 【作者简介】

李耀成 (1997—), 男, 广西北流人, 硕士研究生, 助理研究员, 研究方向: FPGA 高速总线设计、FPGA 图像采集和处理。

常可铮(1997—), 男,河南唐河人,硕士研究生,助理研究员,研究方向:深度学习图像处理、模型量化及FPGA硬件加速。

杨得武 (1997—), 男, 甘肃白银人, 硕士研究生, 助理研究员, 研究方向: 硬件电路设计。

(收稿日期: 2024-09-12)