# 基于 SOC+CX9261A 的国产化信号处理硬件平台设计

万志卫<sup>1</sup> 盛 磊<sup>1</sup> 解 磊<sup>1</sup> WAN Zhiwei SHENG Lei XIE Lei

# 摘要

针对无线通信系统信号处理平台提出的通用化及国产化的要求,文章提出了一种基于 SOC 和 CX9261A 的国产化通用信号处理平台解决方案。系统硬件平台主要由 SOC 控制器 FMQL45T900 和捷变频收发器 CX9261A 芯片组成,结合软件无线电设计思路,实现了载波可变、调谐带宽灵活的通用信号处理硬件平台设计。

关键词

信号处理; 国产化; SOC; CX9261A; 捷变频收发器

doi: 10.3969/j.issn.1672-9528.2025.09.026

#### 0 引言

现代无线通信系统的通信体制越来越灵活多变<sup>[1]</sup>,依靠更换硬件来实现产品的升级及多场景应用,已难以满足日趋复杂的通信功能需求和日渐提高的传输指标要求。软件无线电(software define radio, SDR)是一种基于软件定义的无线通信协议而非通过硬件更新来实现通信系统升级的无线通信技术,能够大大降低通信系统的更新换代成本。信号处理硬件平台作为软件无线电系统的硬件

基础,硬件本身需要具备可编程能力,但长期以来信号处理 硬件平台的核心器件捷变频收发器和信号处理主控芯片一直 被国外产品占据,通信领域事关国家安全,因此,自主可控 国产器件替代必然成为一种趋势 [2-6]。

# 1 系统总体架构设计

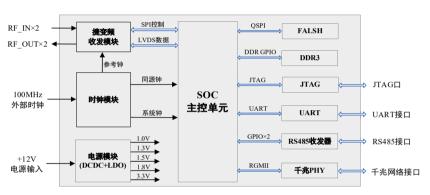

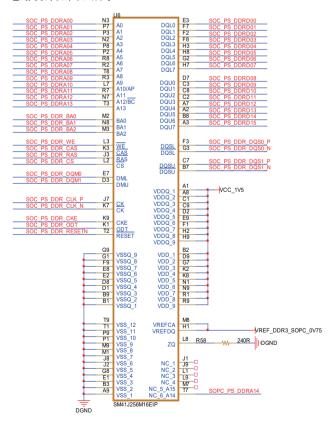

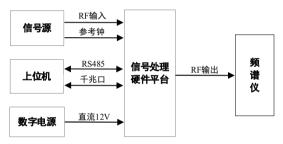

信号处理硬件平台基于 FMQL45T900+CX9261A 硬件架构,主要由捷变频收发模块、SOC 主控单元、时钟电路、接口电路和电源模块等组成。捷变频收发器 CX9261A 完成射频信号的接收和生成;SOC 器件 FMQL45T900 完成捷变频收发器采集的数字基带信号预处理并生成捷变频收发器所需的波形数据;时钟电路主要为捷变频收发器和 SOC 主控器提供采样时钟、同源钟和系统工作钟;接口电路提供系统所需的调试 JTAG 和 UART、控制命令收发 RS485 接口及数据记录千兆网口;电源模块主要将外部输入的直流 12 V 电压转换为内部各模块所需的 3.3、1.8、1.5、1.3 V 等电压,系统硬件框图如图 1 所示。

图 1 信号处理硬件平台系统框图

#### 2 单元电路设计

#### 2.1 捷变频收发器

CX9261A 是一款基于软件无线电理念设计的宽窄带融合、高性能、多通道射频收发器,其工作频率范围为30 MHz~7 GHz,可调谐通道带宽为20 kHz~75 MHz。CX9261A 的接收通道采用直接变频架构,由衰减器、混频器、可编程增益放大器、带宽可调滤波器和高速高精度16 bit-ADC组成,接收通道集成QEC校准功能<sup>[7]</sup>;发射通道采用直接变频架构,由混频器、可编程增益放大器、带宽可调滤波器和高速高精度16 bit DAC组成。发射通道具有本振泄漏校准、IQ 正交校准,能够实现更优的本振泄漏和镜像抑制。

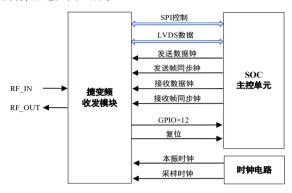

CX9261A 外部接口包含模拟差分输入/输出接口、参数配置接口、数据输入/输出接口、时钟接口和状态指示 GPIO接口。模拟差分输入/输出接口主要用于模拟射频信号的差分接收和输出;参数配置接口为 SPI 接口,支持三线和四线模式,SPI 的最大工作频率为 50 MHz;数据输入/输出接口支持单端 LVCMOS 电平或差分 LVDS 电平,可工作于 FDD模式和 TDD 模式,FDD 模式允许收发同时工作,TDD 模式下收发交替工作,数据接口与主控 SOC 的 PL 端互连,CX9261A 射频接收时,将采样数据发送给 SOC,CX9261A

<sup>1.</sup> 贵州航天电子科技有限公司 四川成都 610000

射频发射时,接收 SOC 波形数据;时钟接口包括参考时钟、本振时钟、数据收/发时钟和数据收/发帧时钟,数据时钟和帧时钟同步工作,保证收发数据的对齐;状态指示 GPIO 口为 12 线 LVCMOS 单端接口,主要用于指示内部 PLL 的锁定状态、接收溢出和内部 AGC 等工作状态的指示,CX9261A 外围硬件互连如图 2 所示。

图 2 CX9261A 外围电路互连设计

#### 2.2 SOC 最小系统

# 2.2.1 主控 SOC 选型

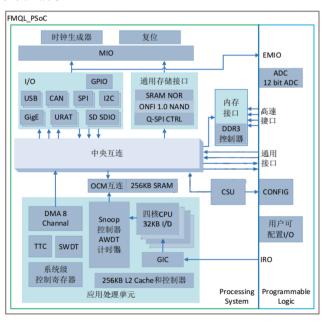

主 控 SOC 选 用 复 旦 微 电 子 公 司 的 高 性 能 芯 片 FMQL45T900,FMQL45T900 单芯片集成了四核高性能处理器的处理系统(PS)和可编程逻辑(PL),四核 CPU 是处理器系统的核心,最高工作频率可达 1 GHz<sup>[4]</sup>,单核独立拥有 32 kB 指令缓存和 32 kB 数据缓存;PL 端具有 28 000 的可编程单元,900 个 DSP 单元、16Lane 高速收发器及 360 个可编程 I/O,与片上存储器、外部存储器 DDR3 接口、各系统功能组件、I/O 外设以及可编程逻辑部分等协同工作,共同组成功能丰富的片上可编程系统,其内部功能框图及资源图如图 3 所示。

图 3 FMQL45T900 内部硬件框图

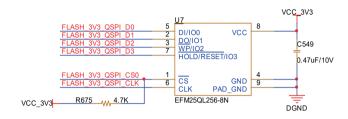

#### 2.2.2 配置 FLASH 电路

主控 SOC 启动配置方式硬件配置为主 QSPI 启动模式, FLASH 选用复旦微 EFM25QL256-E8。EFM25QL256-E8 是 一款 256 Mbit SPI FLASH 存储器,数据读写接口为 SPI 接口, 最高读频率为 100 MHz,工作电压为 3.3 V。硬件电路设计 如图 4 所示。

图 4 EFM25OL256-E8 硬件电路设计

#### 2.2.3 DDR3 缓存电路

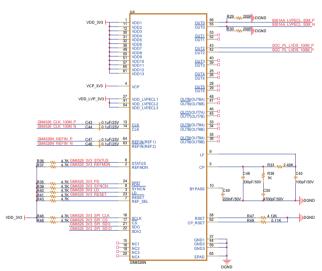

DDR3 缓存电路主要用于 SOC 高速信号处理时的数据缓存 <sup>[5]</sup>,DDR3 外挂在 FMQL45T900 的 PS 端专用 DDR 外设 BANK,系统共配置 2 片 DDR3 器件,总容量为 8 Gbit,位宽为 32 位。DDR3 颗粒选用深圳国微电子的 SM41J-256M16EIP,其单片容量为 4 Gbit,16 位数据位宽,其硬件电路设计如图 5 所示。

图 5 SM41J256M16EIP 硬件电路设计

## 3 时钟电路

时钟电路将外部输入的高性能 100 MHz 时钟生成主控

SOC 和捷变频收发器所需的系统工作时钟(50 MHz)、采样参考时钟(50 MHz)和数据同源钟(100 MHz)。时钟电路选用成都振芯科技的 GM4526N,GM4526N内部集成了 VCO和 PLL,片上调谐频率范围为 1.75 GHz~2.5 GHz,共有 6组 LVPECL输出和 4组 LVDS输出,每一个 LVDS可转换为 2个 CMOS输出,LCVPEL输出频率可达 1.6 GHz,LVDS输出可达 800 MHz,CMOS输出可达 250 MHz,输出时钟可提供亚皮秒级抖动性能。

GM4526N 采用单电源 3.3 V 工作电压,参数配置接通过 SPI 接口实现,SPI 最高工作时钟为 25 MHz; 时钟输入分为 REFINP/REFINPN 差分输入和外部 VCO 时钟 CLKP/CLKN 差分输入,REFINP/REFINPN 差分输入时启用内部 PLL 和 VCO,锁定时通过 LD 引脚指示,VCO 滤波环路参数可根据 实际应用调整,硬件前期设计可采用典型参数或借用厂家提供的仿真软件来确定所需电阻和电容大小值;CLKP/CLKN 差分输入时内部 PLL 和 VCO 不工作,只启用内部的分频电路,用于时钟分频输出,GM4526N 外围硬件电路设计如图 6 所示。

图 6 GM4526N 硬件电路设计

## 3.1 接口电路

信号处理硬件平台外部接口包括UART接口、JTAG接口、RS485接口和千兆PHY接口。UART接口主要用于PS端调试信息的打印;JTAG接口用于程序下载和在线调试仿真;RS485接口用于控制命令的收发;千兆网络接口用于采集实时数据的输出,作为系统数据记录口。UART接口、JTAG接口和RS485接口为常用接口,本文不做详细阐述,主要进行千兆PHY硬件设计说明。

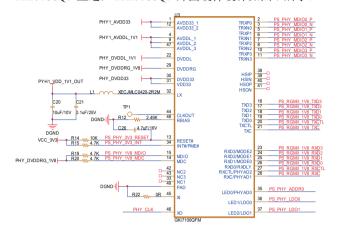

千兆 PHY 选用贵州航天控制的 GKI7100QF, 其是一款高度集成的千兆 PHY, 可同时支持 10Base-Te、100Base-TX、1000Bse-T、100Base-FX、1000Base-X 等 IEEE802.3 标准接口,器件与 MAC 之间通过 RGMII 或者 SGMII 接口通

信,管理接口为 MDIO/MDC,具有工作速率和收发指示功能。本系统借助 SOC 主控器 PS 端自身的 RGMII 外设接口与GKI7100OF 互连,GKI7100OF 外围硬件设计如图 7 所示。

图 7 GKI7100QFM 硬件电路设计

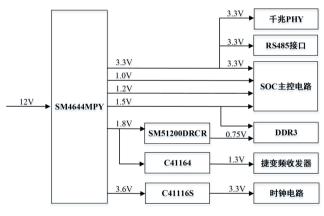

#### 3.2 电源电路

电源电路主要由数字电源和模拟电源两部分组成,本系统的数字电源采用 DC-DC 转换器实现,将外部 12 V 转换为数字电压以及模拟电路所需的中间电压,数字电压包括 3.6、3.3、1.8、1.5、1.2、1 V 等工作电压;时钟和捷变频收发器对纹波要求较高,需采用高电源 PSRR 的 LDO 芯片供电,将数字 3.6 V 和 1.8 V 电压分别转换为 3.3 V 和 1.3 V,系统电源拓扑如图 8 所示。

图 8 电源拓扑设计

DCDC 转换器选用深圳国微电子的 SM4644MPY, 其是一款四通道降压型电源模组,支持四路独立或并联电压输出,单通道 4 A 或四通道并联 16 A 电流输出,宽输入电压范围为 4.5~14 V,输出电压范围为 0.6~5.5 V,主要提供数字电压及 LDO 所需的中间电压。

LDO 器件包括国微电子的 SM51200DRCR 和浙江航 芯源的 C41116S 及 C41164。SM51200DRCR 是一款专用于 DDR、DDR3 的总线端接电源,用于生成本系统 SOC 的缓存 器 DDR3 所需的 0.75 V 端接电压; C41164 输入电压范围为 1.1~1.98 V,输出电压范围为 0.7~1.5 V,最大输出电流 4 A, 具有超高 PSRR 和超低噪声指标,为捷变频收发器提供模拟 1.3 V 电压; C41116S 输入电压范围为 2.3~6.5 V 内,输出最 高 2 A 电流,可调节 1.2~6 V 输出电压轨,用于生成时钟电 路所需的模拟 3.3 V。

#### 4 测试结果

信号处理硬件平台测试系统搭建如图 9 所示,信号源提供 100 MHz 参考时钟和 RF 输入测试信源;上位机通过 RS485 接口和千兆网口与信号处理模块互连,RS485 接口配置信号处理模块的模拟采样和射频输出工作参数,如设置本振频率、调谐带宽及跳频参数等,千兆口实时将采样的模拟基带数据上传到上位机,用于数据记录;频谱仪用于 RF 输出信号的性能测试;数字电源提供直流 12 V 电压,电流不小于 5 A。

图 9 测试系统搭建框图

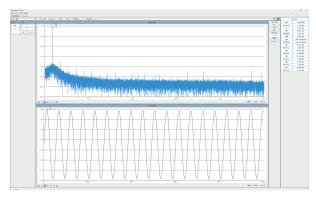

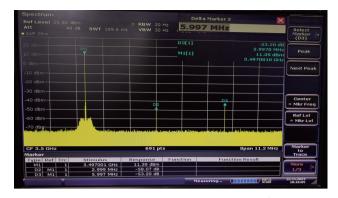

CX9261A 采集模拟信号波形如图 10 所示,输入信号幅度为 8 dBm,信号处理模块本振设置为 3.5 GHz,正交采样信号频率为 1 MHz,采样数据通过上位机软件进行频谱分析,采样单音幅度为 -0.32 dBFS,镜像抑制 61.7 dBc,杂散抑制不小于 65 dBc。CX9261A 射频输出 3.5 GHz 波形如图 11 所示,在输出端增加 15dBm 放大器后,其最大输出电平可达11.39 dBm,输出底噪小于 -70 dBm,近端杂散抑制不小于53 dBc。根据以上测试结果可知,信号处理硬件平台的接收和发射通道性能基本达到 CX9261A 手册性能,若要测试其他频点收发性能,可通过 RS485 接口发送频率更新指令进行响应指标测试。

图 10 CX9261A 采集 3.5 GHz 信号波形及频谱分析

图 11 CX9261A 射频输出 3.5 GHz 信号频谱分析

#### 5 结论

本文介绍了基于全国产化 SOC+CX9261A 的信号处理硬件平台方案,实现了载波和调谐带宽可灵活配置,符合软件无线电的设计思路,针对通信体制多变的无线电收发功能需求,本信号处理硬件平台可缩短设计周期、节约开发成本。实际测试结果表明,该设计方案实现了通用化信号处理平台的硬件设计,具有软件无线电系统所需的宽频带射频收发功能,该硬件平台已在型号产品中应用,性能稳定可靠,在工程应用具有一定参考价值。

#### 参考文献:

- [1] 邓兵,张韫,李炳荣.通信对抗原理图及应用[M].北京: 电子工业出版社,2017:3-4.

- [2] 安超群, 李飞, 陈佳鑫. 基于 CX9261 的国产化软件无线 电硬件平台研究与设计 [J]. 无线互联科技, 2023(17):12-15.

- [3] 左大林. 基于 Zynq 的软件无线电中频处理模块硬件设计 [D]. 成都: 电子科技大学, 2019.

- [4] 陈坤,朱君.一种基于国产 PSOC 的通用硬件平台设计 [J]. 现代信息科技,2020,4(24):46-49.

- [5] 景德胜, 陈川, 缑丽敏. 基于国产多核 DSP+FPGA 架构弹载计算机硬件平台设计 [J]. 航空计算技术, 2021,51(6):84-87

- [6] 杨新宇.AD9371 软件无线电硬件平台设计与实现 [J]. 电子元器件与信息技术, 2020,4(2):61-62.

- [7] CX9261A 宽窄融合射频收发器数据手册 [M]. 杭州: 杭州城 域 科技有限公司, 2023.

#### 【作者简介】

万志卫(1985—), 男, 江西鹰潭人, 硕士研究生, 研究方向: 信号处理。

(收稿日期: 2025-04-16 修回日期: 2025-09-10)