# 基于 FPGA 的智能化串口通讯模块设计

王永国<sup>1,2</sup> 印 通<sup>1</sup> 刘媛媛<sup>1</sup> 李 爽<sup>3</sup> WANG Yongguo YIN Tong LIU Yuanyuan LI Shuang

# 摘要

针对现有串口通讯设计中存在的无法满足高实时、高并行化需求的问题,文章设计了一种基于 FPGA 的智能化串口通讯模块。通过将双口存储器、串口通讯协议和核心控制逻辑集成到 FPGA 内部,实现多通道 RS422 串行数据的高效并行处理。同时,为匹配 FPGA 设计高并行化的特点,将双口存储器资源根据功能应用进行拆分,结合智能化控制流程原理进行重新组合设计,使得 UART 各通道可以独立并行工作,各通道串口通信数据通过双口存储器与 CPU 模块进行交互,从而增加数据并行化处理程度,提高处理器效率。实验表明,智能化串口通讯模块设计正确,在一定程度上提高了处理器效率,满足了设计需求。

关键词

FPGA; 串口通讯; 智能化

doi: 10.3969/j.issn.1672-9528.2025.03.020

## 0 引言

随着通讯技术的不断发展,现场可编程器件(field programmable gate array, FPGA)因其具有集成度高、体积小、功耗低、高可靠性、高安全性、系统成本低、灵活性好、便于连接等特点,在通讯技术领域中得到广泛应用,常用通讯方法包括串口通讯。

文献 [1] 基于 FPGA 技术设计了一种异步串口通信波特 率自动检测方法,可实现快速、准确检测异步串口通信的波 特率值。文献[2]对串口协议进行研究,介绍串口设计中的 关注点,根据目前的项目对基于 FPGA 的串口设计进行详细 说明。文献 [3] 基于 FPGA 实现了串口数据接收模块采集多 串口数据,并通过控制寄存器达到控制通信数据波特率的目 的,实现了8个串口数据的传输,并且具有较高数据接收成 功率。文献[4]引入了多路串口数据的同时采集、缓冲及打 包的数据流处理思想,采用基于 FPAG+ 多串口 +USB 的硬件 框架结构及总线不同速率的传输软件处理算法,实现了多路 串口数据的采集与传输。 文献 [5] 提出一种基于国产化 FPGA 实现的智能串口通讯方法及系统,详细描述了国产化 FPGA 中实现串口通讯的设置方法和思路。文献 [6] 基于 zynq 架 构的控制器能够较好实现单个控制器对多条串行数据通道的 并行化控制,同时能够通过软件对底层串口的通讯参数进行 配置,其中,zynq处理器集成了CPU功能和FPGA功能, 其中智能串口在 zynq 中的 FPGA 中实现, 传统 CPU 架构对

目前比较通用的串口通讯实现方案有两种。一是采用串口通讯芯片实现串口通讯,使用 CPLD 实现上位机与串口通讯芯片之间的逻辑控制,完全基于上位机接收和发送数据;二是采用 FPGA 实现专用串口扩展芯片的功能,通过在FPGA 内部集成多路串口控制器,上位机主程序通过控制串口控制器的工作,实现串行数据的接收和发送。当数据量大时,上述两种方案中,上位机主程序需要频繁地进行中断响应或者进行标志位查询操作,控制数据接收流程并缓存收到的数据,占用上位机的时间较长;在发送数据时,需要查询当前串口通讯状态,进行发送流程控制,会占用上位机大量的时间,从而影响上位机的工作效率。在多串口通道设计中,上位机需采用串行方式依次扫描各个通道,当串口通讯速率过低时导致上位机等待时间过长,难以满足实时性要求较高且需要并行处理的实际需求。针对上述问题,本文提供一种基于 FPGA 的智能化串口通讯模块设计方案。

文献 [7] 具体涉及一种基于 FPGA 架构的智能串口通讯模块及控制方法,利用 FPGA 并行处理的特点,通过设计可复用的串口通道逻辑单元以及智能化控制管理逻辑单元,实现多串口通道通讯数据的并行接收、发送和自测试功能。设计具备完备的 BIT 策略和接口防护功能,克服了传统串口通讯模块设计 CPU 负荷重、FPGA 引脚数量多的缺点,提高CPU 有效利用率和串行总线数据传输带宽,具备较强理论意义和实用价值。本文在文献 [7] 基础上对 FPGA 内部实现智能串口的三大部分逻辑(LBE 局部总线解析逻辑、命令解析逻辑和 UART 通道逻辑)进行详细分析和仿真验证。

于多通道并行性控制较差的问题。此外,相较于波特率等固定参数的串口传输方式更灵活的优势,具备将软件控制端和 FPGA控制端集成在一起,可以有效减少器件布板面积。

<sup>1.</sup> 中国航空工业集团公司西安航空计算技术研究所 陕西西安710065

<sup>2.</sup> 西北工业大学计算机学院 陕西西安 710100

<sup>3.</sup> 山东省网络安全与信息化技术中心 山东济南 250000

## 1 硬件结构设计

智能化串口通讯模块实现了 10 路 RS422 串行接口的接口信号处理、协议处理及对数据的智能化管理, 其智能化的设计原理是在 FPGA 并行运算的基础上, 将双口存储器、串口通讯协议和核心控制逻辑集成到 FPGA 内部, 通过核心控制逻辑的设计, 实现多通道 RS422 串行数据的并行处理, 并将处理结果存放在对应的双口存储器中供 CPU 模块读取。

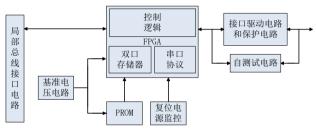

本模块硬件设计主要由局部总线接口电路、FPGA可编程逻辑及其外围相关配置电路、RS422接口驱动和保护电路,以及自测试电路四部分组成,图1为本模块电路硬件结构框图。

图 1 电路硬件结构框图

总线接口电路采用标准 LBE 总线接口电路,实现与CPU 之间的通讯。

FPGA 可编程逻辑及其外围相关配置电路主要包括可编程逻辑 FPGA 芯片电路,复位电源监控电路,为 FPGA 提供工作电压的基准电压电路和 PROM 存储器电路。

RS422 接口驱动和保护电路采用开路和短路 Fail\_safe 端接方式(open-line and shorted-line fail-safe termination),并在接收端并联端接匹配电阻以消除传输线上的信号反射,减小通讯故障率。开路和短路 Fail-safe 端接方式可以使当接收器端开路或短路时,接收器输入差分电压大于 200 mV,其输出确定状态(高电平)。

自测试电路完成 UART 通道外回绕测试功能,通道内回绕测试通过 FPGA 内部的串口协议直接进行回绕测试,外回绕测试通过外回绕测试命令控制外部切换开关使得 RS422 收发器的接收端与发送端相连进行回绕测试。

### 2 逻辑架构设计

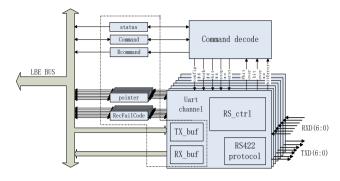

# 2.1 逻辑架构原理

为满足设计要求,同时考虑到 FPGA 逻辑设计并行性的特点,将双口存储器资源根据功能应用进行拆分,结合智能化控制流程原理进行重新组合设计,使得 UART 各通道可以独立并行工作。模块 FPGA 设计原理框图如图 2 所示。基于 FPGA 的智能化串口通讯逻辑原理框图内部主要分为三大部分逻辑: LBE 局部总线解析逻辑、CPU 命令解析逻辑和 UART 通道逻辑。其中虚线框表示双口存储器,设计

中将其按功能进行拆分为不同功能的寄存器和发送 / 缓冲双口存储器。

图 2 基于 FPGA 的智能化串口通讯逻辑原理框图

### 2.2 LBE 局部总线逻辑

LBE 局部总线逻辑完成 LBE 局部总线协议信号的解析功能, CPU 可对本模块进行 8 位数据访问,该访问数据可以是存储器数据,也可以是 I/O 数据。

# 2.3 CPU 命令解析逻辑

CPU 命令解析逻辑完成 CPU 命令的解析功能,根据解析的命令产生不同的功能信号,这些信号包括正常工作(work)信号、停止(stop)信号、自测试(bit)信号、软复位(srst)信号,同时根据各 UART 通道返回的状态信息,完成各状态字寄存器的信息更新。

## 2.4 UART 通道逻辑

UART 通道逻辑主要完成上电时 UART 配置初始化、上电 BIT 测试,并在 CPU 命令控制信号的作用下完成相应的功能,并返回通道状态信息。

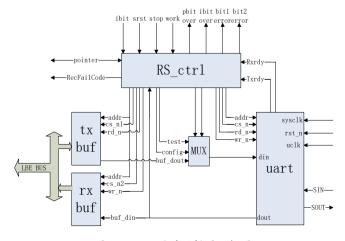

串口通道逻辑包括五部分逻辑单元:发送缓冲区逻辑单元、接收缓冲区逻辑单元、UART IP 核逻辑单元、数据通路选择逻辑单元和通道核心控制逻辑单元。其中通道核心控制逻辑单元在 CPU 命令控制信号下控制通道内各功能逻辑单元之间协同工作,完成相应的功能。UART 通道逻辑的原理框图设计如图 3 所示。

图 3 UART 通道逻辑原理框图

UART 通道逻辑主要包含五部分功能逻辑:

- (1) tx buf 逻辑: 通道发送缓冲区,缓冲区大小为 256 Byte,缓存区大小可根据实际使用动态进行配置,128、 256、512 Byte 等均可以,字节需大于 UART 各通道接收的 数量。

- (2) rx buf 逻辑: 通道接收缓冲区,缓冲区大小为 256 Byte,缓存区大小可以动态设置。

- (3) UART 逻辑: UART 串口通讯协议 IP 核,该通讯 协议IP具备可配置波特率、校验方式、数据长度、停止位 等信息。

- (4) MUX 逻辑:数据通路选择逻辑,根据通道的工作 状态,选择不同的数据信息发送至 UART 逻辑,这些数据信 息包括 UART 配置信息、通道自测试数据、正常发送数据。

- (5) rs ctrl 逻辑: 通道核心控制逻辑, 在 CPU 命令解 析逻辑产生的控制信号的作用下,控制通道内各功能逻辑单 元之间协同工作,完成相应的控制功能。

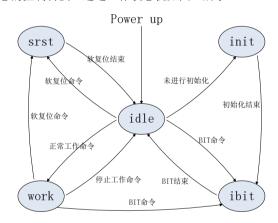

文中设计了通道工作状态机,包括空闲状态、初始化状 态、自测试状态、正常工作和软复位,以实现通道不同工作 状态的控制转换。通道工作状态机如图 4 所示。

图 4 UART 通道工作状态机

UART 通道工作状态机中共有5个工作状态,分别为 idle 状态、init 状态、ibit 状态、work 状态和 srst 状态。

空闲状态: idle 状态为通道空闲状态,模块上电后通道 的默认状态,表示当前处于空闲状态,或者收到 CPU 停止命 令后进入 idle 状态表示停止工作状态,等待 CPU 新的命令进 入新的工作状态。

初始化状态: init 状态为通道初始化配置工作状态,对 UART 波特率等配置信息进行配置初始化。

自测试状态: ibit 状态为通道 BIT 测试工作状态。通道 有两种 BIT 测试,一是上电 BIT(PBIT) 测试,即通道上电初 始化完成后,进行 UART 通道内循环及外循环测试过程,并 报告 BIT 测试结果; 二是维护 BIT(IBIT) 测试, 即收到 CPU 的 IBIT 命令后, 进行 UART 通道内循环及外循环测试过程,

并报告 BIT 测试结果。由于 PBIT 和 IBIT 的不同点在于启动 触发条件和执行次数不一致,但其测试结果存放在相同的状 态字寄存器中,因此可将 PBIT 和 IBIT 合并到一个状态内, 通过控制信号以区分两种 BIT。

软复位状态: srst 状态为通道软复位状态, 对通道内部 分资源进行软复位操作,资源包括:通道BIT状态字、接收 发送指针和通道故障寄存器。

正常工作状态: work 状态为通道正常工作状态, 处于此 状态下的 UART 通道根据接收和发送指针及 UART 的状态完 成相应的 UART 接收和发送过程,并更新收发指针信息。

通道工作状态机各状态之间的转换关系为:

- (1) 当模块上电后各通道默认进入 idle 状态, 然后进 入 init 状态对 UART 进行配置。

- (2) init 配置工作完成后进入 ibit 状态进行通道上电 BIT 测试,并上报 BIT 测试结果。

- (3) 上电 BIT 测试完成后进入 idle 工作状态,表示通 道处于空闲状态, 等待 CPU 新的命令, 并根据 CPU 新的命 令分别进入 work 工作状态、srst 软复位状态、ibit 维护 BIT 状态。

- (4) ibit 维护 BIT 测试完成后进入 idle 状态。

- (5) srst 复位结束后进入 idle 状态。

- (6) 当工作在 work 状态时, 收到 CPU 停止命令则进 入 idle 状态, 收到软复位命令则进入软复位状态, 收到 ibit 命令则进入 ibit 状态。

## 2.5 架构运行方式

本架构基于FPGA的智能化串口通讯逻辑工作原理如下:

- (1) 上电后, FPGA 逻辑自动完成内部各单元结构的 初始化过程,整个串口模块处于规定的缺省工作模式,初始 化过程包括初始化双口存储器单元和初始化配置串口协议 IP 核,以及内部各寄存器的初始化配置。

- (2) 初始化完成后,在通道控制逻辑单元的控制下, 各串口通道逻辑自动完成上电自测试过程,以保证模块工作 在正确的方式中,测试内容主要为 UART 通道内回绕测试 和外回绕测试。当上电自测试出错时,则进行不超过3次的 自测试过程,并发送自测试状态信息给 CPU 命令解析逻辑 单元。

- (3) 上电自测试结束后, CPU 读取上电自测试结果, 并通过局部总线向 FPGA 逻辑发送 CPU 命令字数据。

- (4) LBE 局部总线解析逻辑完成局部总线信号的解析, 并将解析后的 CPU 命令存储在命令寄存器中,供 CPU 命令 解析逻辑讲行解析处理。

- (5) CPU 命令解析逻辑根据解析处理的 CPU 命令,产 生相应的命令控制信号发送给各串口通道逻辑单元,控制各 通道完成相应的工作。命令控制信号包括初始化信号、正常

工作信号、停止工作信号、自测试信号、软复位信号。

(6) UART 通道逻辑根据命令控制信号控制串口通道 逻辑内各逻辑单元之间协调工作,完成相应的串口功能,并 返回相应的状态信息。UART 通道逻辑实现数据接收,接收 数据放在接收缓存区,根据上位机 CPU 读取指令,LBE 局 部总线解析逻辑和 CPU 命令解析逻辑将数据取出;根据上位 机 CPU 发送数据指令,上位机 CPU 编写数据,将上位机数 据发送到 LBE 总线中, LBE 局部总线解析逻辑和 CPU 命令 解析逻辑将发送数据写入到 UART 通道逻辑的发送缓存区, UART 通道逻辑将发送缓存区的数据发送出去。

## 3 仿真验证

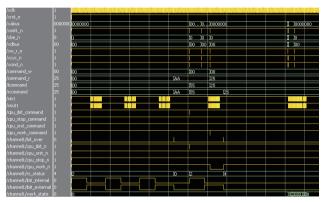

对整个逻辑编码设计后,使用 Modelsim 对其进行仿真, 通道工作状态机仿真结果如图 5 所示。

图 5 诵道工作状态机仿真

图 5 中,通道上电 BIT 结束后,收到 CPU 的 IBIT 命令, 进入 ibit 工作状态, 在 ibit 状态期间, 收到 CPU 的正常工作 命令,则将命令锁存,在BIT结束后,再响应CPU的正常 工作命令, 进入正常工作状态。

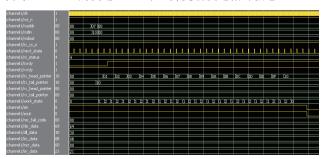

图 6 为串口通道发送仿真过程,在 UART 工作空闲时, 当 CPU 更新了发送指针后,识别到发送缓冲区有待发送数据, 且 UART 发送器处于空闲状态,则将发送缓冲区中的数据依 次写入 UART 的发送 FIFO 中,并更新发送指针信息。

图 6 串口通道发送仿真

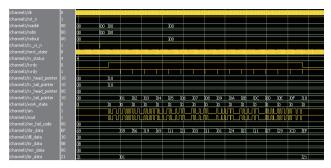

图 7 为串口通道接收时仿真, 当 UART 工作空闲时, 识 别到接收缓冲区不满且 UART 接收 FIFO 中有数据,则将接 收FIFO中的数据读取到接收缓冲区中,并更新接收指针信息。

图 7 串口通道接收仿真

从上述三张仿真图中可以看出, 仿真结果与预期设计结 果一致,满足设计要求。

#### 4 结语

本文提供了一种基于 FPGA 的智能化串口通讯模块设计 方案,通过在 FPGA 内部采用智能化管理设计方法,并行处 理完成多通道串口通讯数据的接收、发送和自测试过程,从 而减少占用处理器时间,提高处理器效率;同时处理结果通 过内嵌的双口存储器实现与处理器之间的数据交互,提高数 据处理能力。通过功能仿真对该设计进行验证,仿真结果表 明,该方法设计正确,可以满足设计要求。

### 参考文献:

- [1] 陈虎. 基于 FPGA 的异步串口通信波特率自动检测技术 [J]. 应用科技, 2023, 50(2):60-65.

- [2] 张诚, 孙列鹏, 肖薇, 等. 基于 FPGA 的串口实现 [J]. 软件, 2018, 39(11): 219-223.

- [3] 王春媚. 多串口并行通信数据传输系统设计 [J]. 现代电子 技术, 2017,40(4):86-90.

- [4] 郭敏, 庄信武, 王向东, 等. 基于 FPGA 的多通道串口数 据采集与传输设计 [J]. 计算机测量与控制, 2017, 25(11): 186-189.

- [5] 鹍骐科技(北京)股份有限公司. 一种基于国产化 FPGA 实现的智能串口通讯方法及系统:CN202210248837.2[P]. 2023-11-28.

- [6] 天津津航计算技术研究所. 一种基于 zynq 的多通道串口 通讯控制器:CN202311181310.3[P]. 2023-12-01.

- [7] 中国航空工业集团公司西安航空计算技术研究所. 一 种基于 FPGA 架构的智能串口通讯模块及控制方法: CN201611154109.6[P]. 2018-06-29.

## 【作者简介】

王永国(1988-), 男, 陕西西安人, 博士研究生, 高 级工程师,研究方向:计算机应用。

(收稿日期: 2025-03-08)